# Designing Cards and Drivers for the Macintosh Family

by Apple Computer, Inc.

## Third Edition

# Designing Cards and Drivers for the Macintosh Family

Third Edition

# Addison-Wesley Publishing Company

Reading, Massachusetts Menlo Park, California New York Don Mills, Ontario Wokingham, England Amsterdam Bonn Sydney Singapore Tokyo Madrid San Juan Paris Seoul Milan Mexico City Taipei APPLE COMPUTER, INC.

© 1992, Apple Computer, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc. Printed in the United States of America.

Apple Computer, Inc. 20525 Mariani Avenue Cupertino, CA 95014-6299 408-996-1010

Apple, the Apple logo, APDA, AppleLink, AppleTalk, A/UX, EtherTalk, LaserWriter, Macintosh, MPW, and SANE are trademarks of Apple Computer, Inc., registered in the United States and other countries.

Applecolor, Apple Desktop Bus, A/ROSE, QuickDraw, and SuperDrive are trademarks of Apple Computer, Inc.

Adobe Illustrator and PostScript are registered trademarks of Adobe Systems Incorporated.

HyperCard is a trademark of Claris Corporation.

IBM is a registered trademark of International Business Machines Corporation.

ITC Garamond and ITC Zapf Dingbats are registered trademarks of International Typeface Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

Motorola is a registered trademark of Motorola Corporation.

NuBus is a trademark of Texas Instruments.

Sony is a registered trademark of Sony Corporation.

Simultaneously published in the United States and Canada.

ISBN 0-201-60855-3 1 2 3 4 5 6 7 8 9-MU-9695949392 First printing, April 1992 LIMITED WARRANTY ON MEDIA AND REPLACEMENT

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, **APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.**

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent,

or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

## **Contents**

Figures and tables / xix

#### **Preface** About This Book / xxxi

Design philosophy / xxxii Conventions used in this book / xxxii The Courier font / xxxiv About the mechanical drawings and design guides / xxxv About the Macintosh technical documentation / xxxv How to get more information / xxxvii APDA / xxxviii User groups / xxxviii Apple Developer Services / xxxix

#### Introduction Expansion Strategy for the Macintosh Family / 1

Limiting the number of expansion interfaces / 2 NuBus expansion / 3 Processor-direct slot (PDS) expansion / 3 The 68000 and 68020 Direct Slot expansion interfaces / 4 The 68030 Direct Slot expansion interface / 5 The 68040 Direct Slot expansion interface / 5 Recommended strategy for 68030 and 68040 Direct Slot expansion card design / 6 Converting your designs / 7 Application-specific expansion / 7

Slot strategy summary / 7

#### Part I The NuBus Expansion Interface / 9

About Part I / 10 Addressing design philosophy / 11 NuBus use and licensing requirements / 12

#### 1 Overview of Macintosh Computers With the NuBus Interface / 13

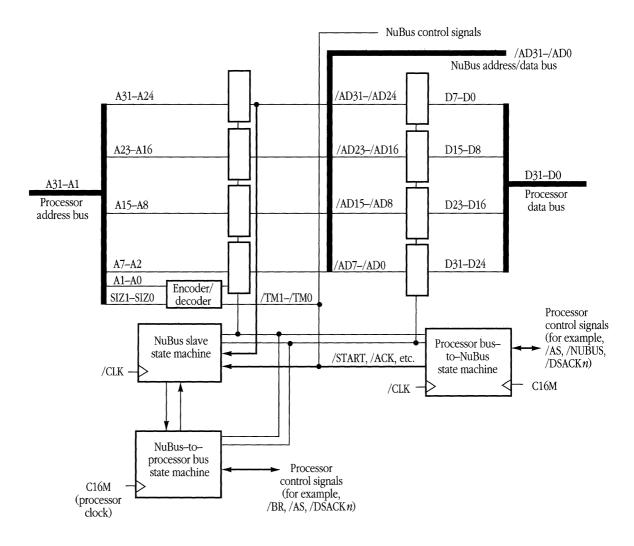

Major features / 14 Hardware architecture / 18 RAM / 28 ROM / 28 Device I/O / 29 Address/data bus / 30 Macintosh IIsi NuBus interface / 31 NuBus interface architecture / 31 Processor bus-to-NuBus state machine / 32 NuBus-to-processor bus state machines / 34

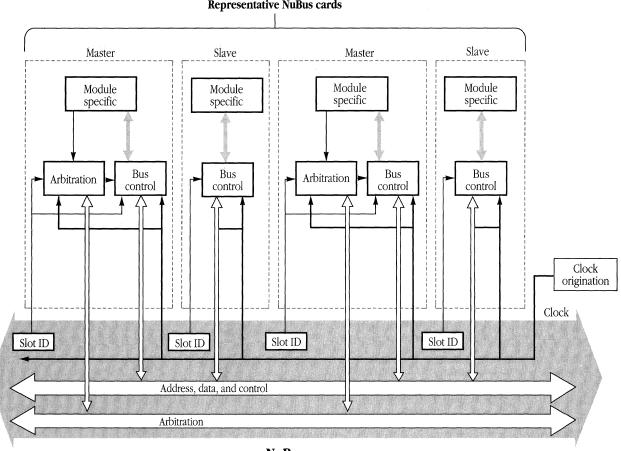

#### 2 NuBus Overview / 37

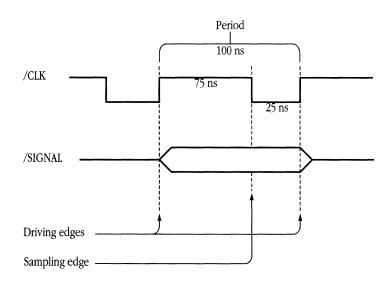

NuBus features / 38 NuBus elements / 39 NuBus '90 features / 41 NuBus signal classifications / 41 NuBus timing / 44 NuBus terminology / 44

#### 3 NuBus Data Transfer / 51

Utility signals / 52 Clock signals / 52 Reset signal / 52 Power fail warning signal / 53 Nonmaster request signal / 53 Serial bus signals / 54 Card slot identification signals / 54 Signal line determinacy / 55 Data-transfer signals / 56 Control signals / 56 Address/data signals / 57 Bus parity signals / 57 Cache-coherency signals / 58 Data-transfer specifications / 58 Single data cycle transactions / 59 Read transactions / 60 Write transactions / 61 Acknowledge cycles / 63 Attention cycles / 63 Interrupt operations / 65 By write transaction / 65 By slots sharing a single NuBus /NMRQ line / 65 By a dedicated /NMRQ line from each slot / 65 1X block data transfers / 66 1X block read / 67 1X block write / 68 1X block transfer errors / 70 2X block data transfers / 70 Signal protocol for 2X block transfers / 71 2X block-transfer flow control / 72 2X block read transfer / 72 2X block write transfer / 75 2X block write transfer with delayed status indication / 79 Cache coherency / 81 Cache line states and sizes / 82 Read and write miss / 82 Snooping / 83 Cache-coherency transactions / 83 ReadShared / 84 ReadExclusive / 84 ReadInvalidate / 85 ReadNosnoop / 85 WriteExclusive / 85 WriteInvalidate / 85 WriteNosnoop / 86 AttentionShared / 86 AttentionExclusive / 86 AttentionInvalidate / 86

Non-cache-coherent transactions to caching modules / 87 Cache-coherent states / 87 Cache-coherent masters / 90 Arbitration by cache-coherent modules / 92 Nonaligned microprocessor accesses / 93 Nonaligned reads / 94 Nonaligned writes / 94 Data caching / 94 Compliance categories / 94

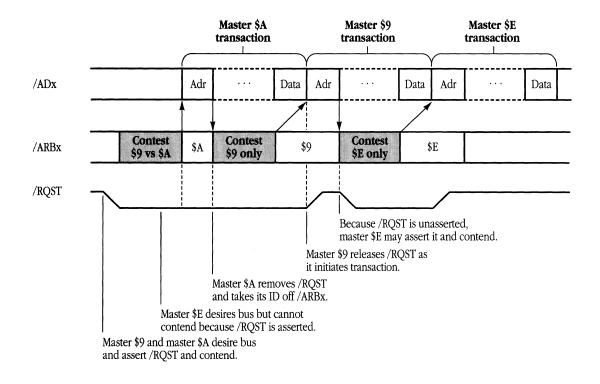

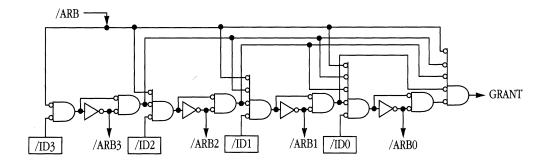

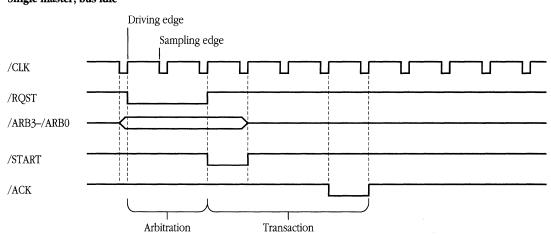

#### 4 NuBus Arbitration / 97

Arbitration overview / 98 Arbitration logic mechanism / 99 Arbitration timing overview / 101 Locking / 101 Bus locking / 103 Resource locking / 104 Bus parking / 105

#### 5 NuBus Card Electrical Design Guide / 107

Electrical requirements / 108 Logical and electrical state relationships / 108 DC and AC specifications for line drive / 108 /PFW interaction with the power supply / 110 NuBus connector pin assignments / 111 Power supply specifications / 113 NuBus power budget / 114 Timing requirements / 116 Utility and data-transfer timing / 116 Arbitration timing / 117

vi Designing Cards and Drivers for the Macintosh Family

#### 6 NuBus Card Physical Design Guide / 119

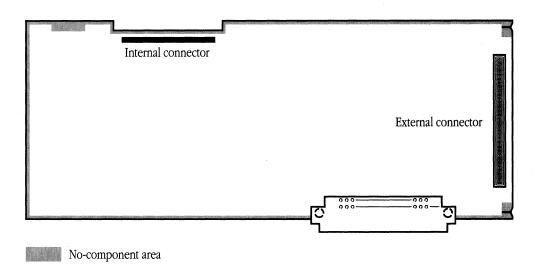

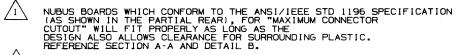

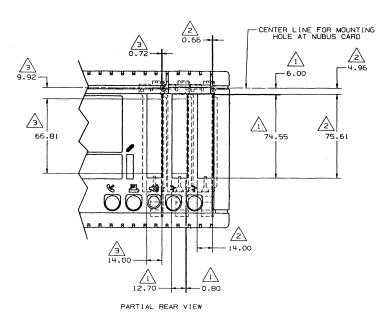

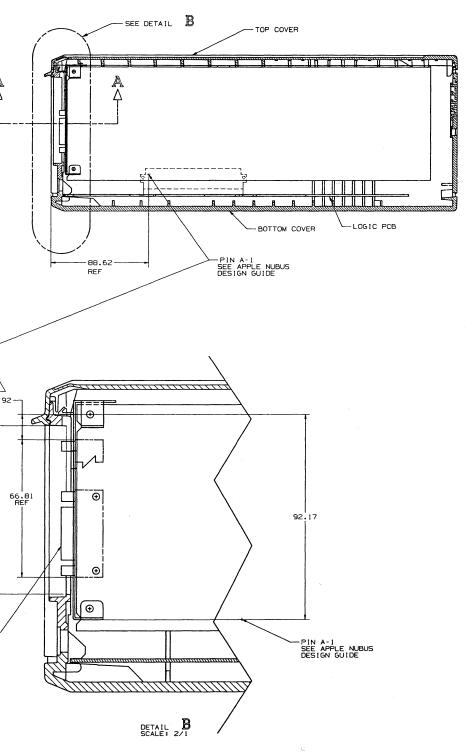

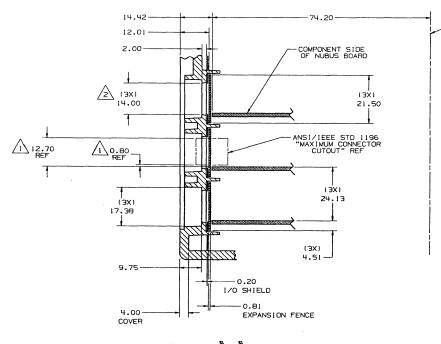

Card description / 120 NuBus connector description / 122 NuBus expansion card internal connectors / 125 Recommended heat dissipation guidelines / 127 NuBus slot ordering / 127 Physical implementation of the Macintosh IIsi NuBus adapter kit / 128

#### 7 NuBus Card Memory Access / 131

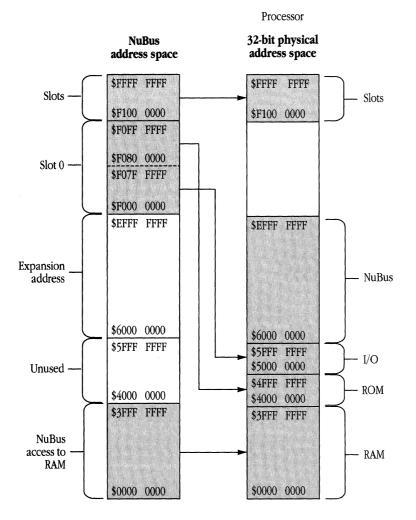

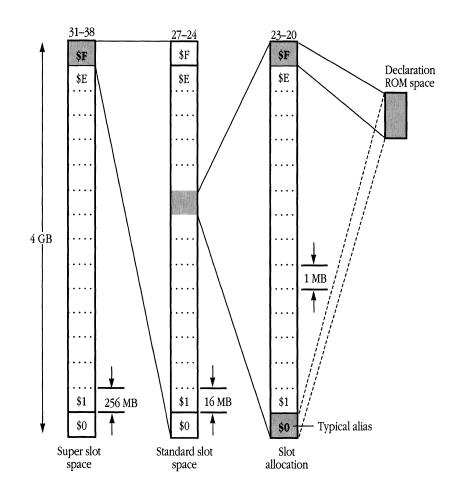

NuBus address space / 132

Address allocations for Macintosh computers with NuBus / 134

Slot allocations / 136

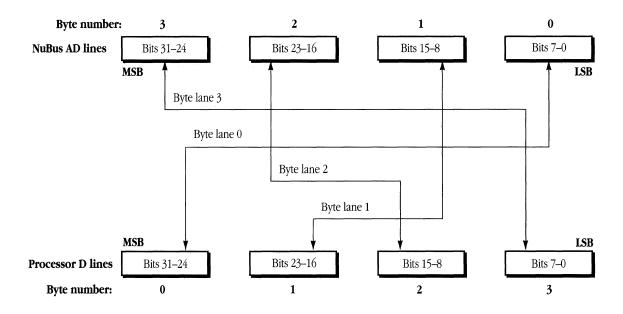

NuBus bit and byte structure / 136

Byte smearing / 138

#### 8 NuBus Card Firmware / 141

An introduction to the firmware / 142

The Slot Manager and the declaration ROM / 142

sResources / 143

How sResources are implemented / 144

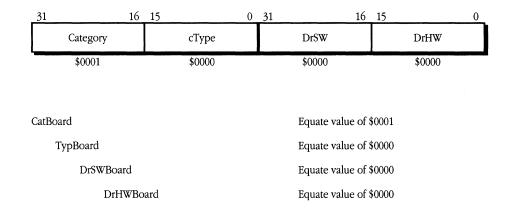

The sRsrcType entry / 145

How to configure the sRsrcType fields for video card sResources / 147

sRsrcType fields for a video card functional sResource / 147 sRsrcType fields for a video card board sResource / 148

How QuickDraw interacts with the Slot Manager and declaration ROM  $\,/\,$  149

Summary of firmware design objectives / 150

Obtaining card identification and sRsrcType values from MacDTS  $\,/\,$  151

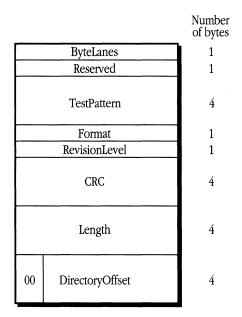

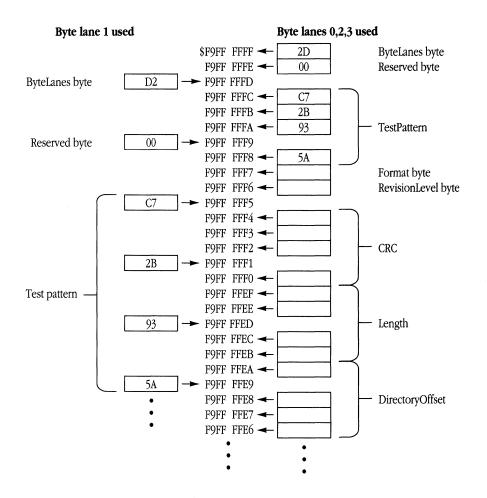

Data types / 152

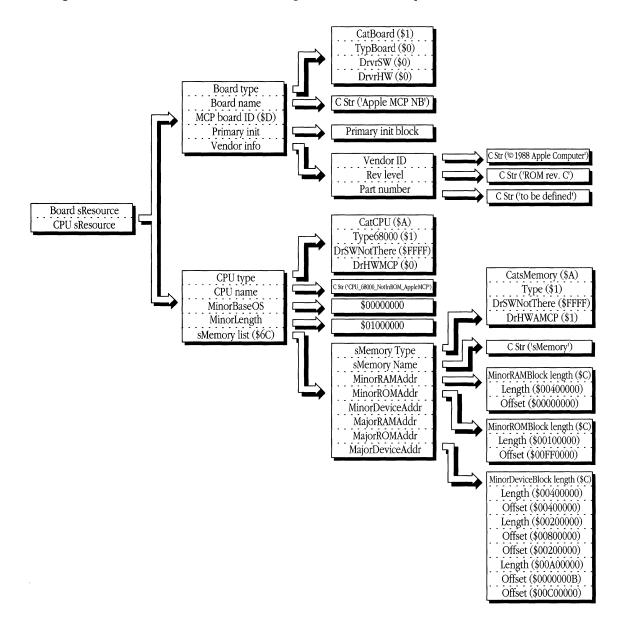

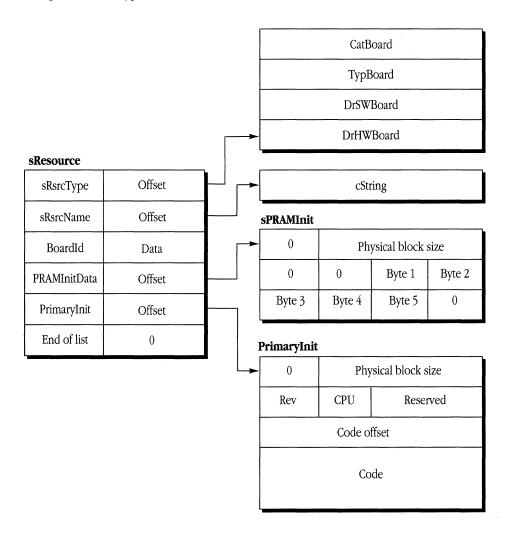

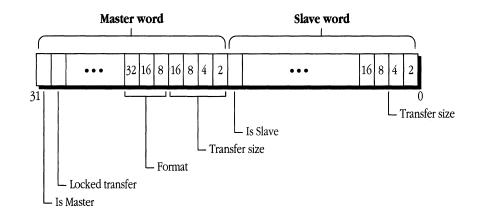

Firmware structure / 153 The format block / 156 ByteLanes / 158 Reserved / 159 TestPattern / 159 Format / 159 RevisionLevel / 159 CRC / 160 Length / 160 DirectoryOffset / 160 The sResource directory / 161 sResource structure / 162 Apple-defined sResource entries / 163 sRsrcType / 165 sRsrcName / 166 sRsrcIcon / 166 sRsrcDrvrDir / 166 sRsrcLoadRec / 167 sRsrcBootRec / 168 sRsrcFlags / 169 sRsrcHWDevId / 169 MinorBaseOS / 170 MinorLength / 170 MajorBaseOS / 170 MajorLength / 170 sRsrcCicn / 170 sRsrcIcl8 / 170 sRsrcIcl4 / 171 sMemory / 171 The board sResource / 174 BoardId / 175 PRAMInitData / 176 PrimaryInit / 176 STimeOut / 178 VendorInfo / 178 SecondaryInit / 179 NuBus block-transfer mode sResource entries / 180 Additional firmware requirements of video cards / 182 Identifying direct devices / 183 Identifying 32-bit addressable configurations / 183 Icons / 184 Apple-defined video sResource entries / 185 sGammaDir / 185 sRsrcVidNames / 185 Gamma table data / 186 Video mode name directory / 186 Video card name / 187 Resolution / 187 Sample code / 187 Macintosh Coprocessor Platform / 188

#### 9 NuBus Card Driver Design / 189

Storing the driver code for a NuBus card / 190 Specific and generic drivers / 190 Card-specific drivers / 190 Card-generic drivers / 191 The sDriver record / 193 Installing a driver at startup / 193 Calling a driver / 195 Slot device interrupts / 197 SIntInstall / 198 SIntRemove / 198 PollRoutine / 198 Video drivers / 200 Video declaration ROM Information / 201 Video driver routines / 202 Video driver data structures / 204 Control routines / 205 Status routines / 211 Gamma correction in Macintosh computers / 213 How gamma correction works / 213 The gamma table data structure / 215 Using gamma correction / 216 Video driver example / 216 Summary / 217 Data types / 217

Interrupt queue routines / 218 Advanced control routines / 218 Status routines / 219 Assembly-language information / 219 Data structures / 219 Interrupt queue routines / 220

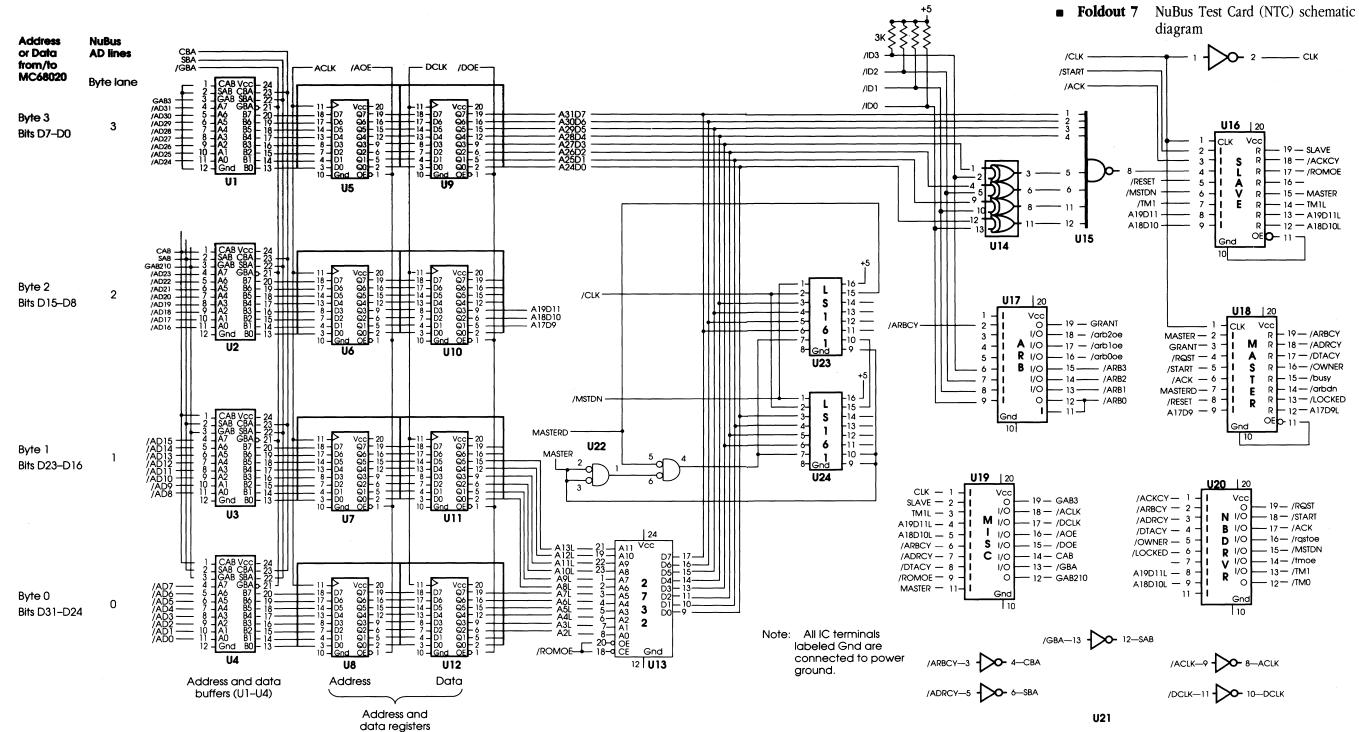

#### 10 NuBus Design Examples / 221

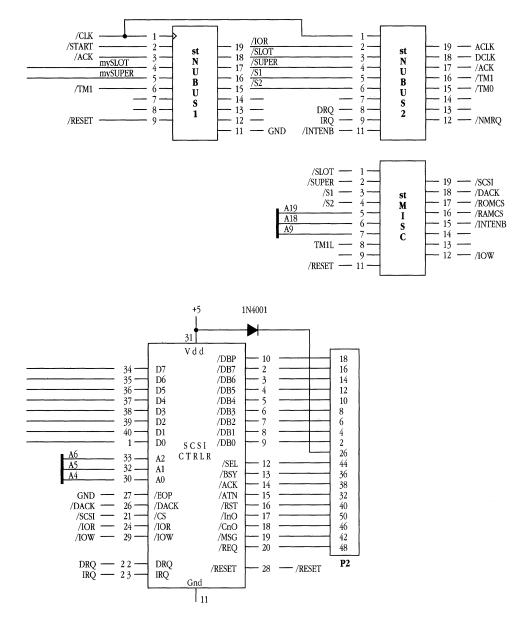

NuBus Test Card / 222 Overview of operation / 222 Programming model / 222 Byte swapping and the NTC / 223 Programming the NTC / 225 Word read (Macintosh computer RAM) / 225 Halfword 0 write / 226 Hardware organization / 226 NuBus address/data buffers / 227 Address and Data registers / 227 Address comparison / 227 SLAVE PAL / 227 ARB PAL / 227 MASTER PAL / 228 MISC PAL / 228 NBDRVR PAL / 228 Slave operation / 230 Master operation / 230 SCSI-NuBus Test Card / 231 Software overview / 231 Hardware overview / 231 NuBus transceivers (ALS651's) / 234 Slot Decode (F86/F30) / 235 NuBus state machine (stNUBUS1 PAL) / 235 NuBus signal generator (stNUBUS2 PAL) / 235 Decode and timing (stMISC PAL) / 235 SCSI chip (NCR5380) / 235 Pseudo-ROM / 236 RAM / 236 PAL descriptions / 236

х

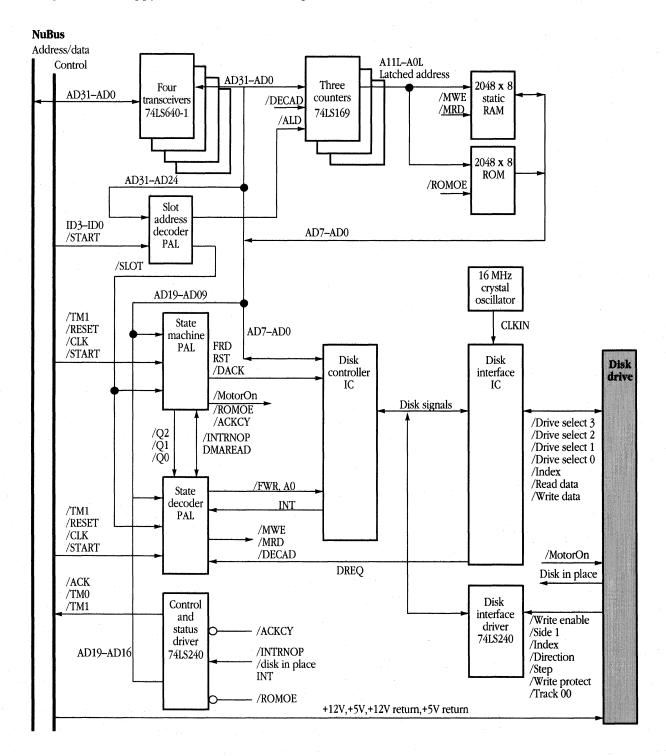

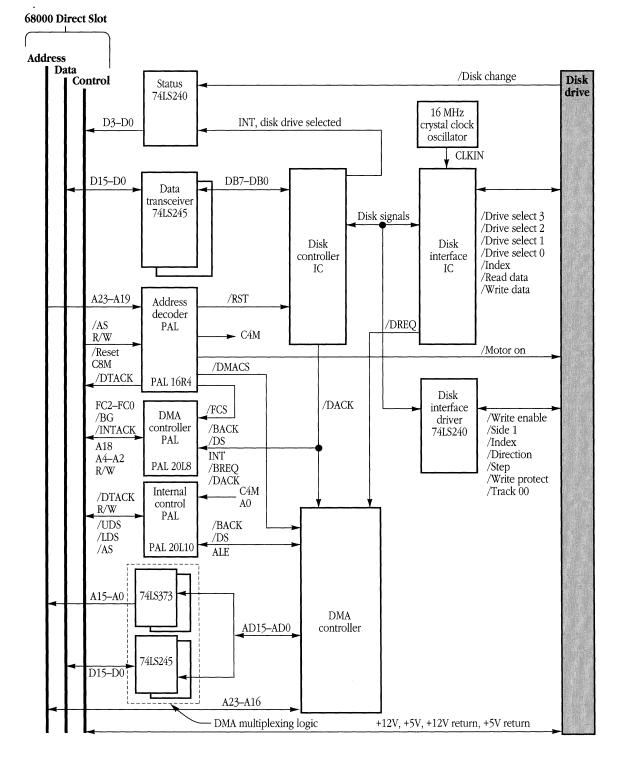

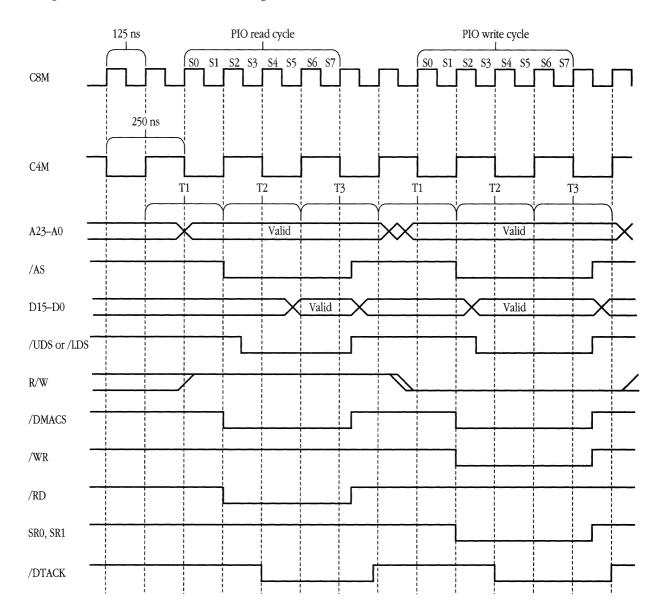

A simple disk controller / 236 System configuration / 236 Controller card block diagram / 237 Floppy disk controller logic / 239 NuBus interface logic / 239 Programmed I/O operations / 240 On-card DMA operations / 241 Memory map and the declaration ROM / 242

#### 11 The Macintosh II Video Card / 245

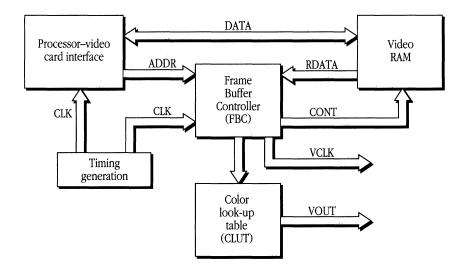

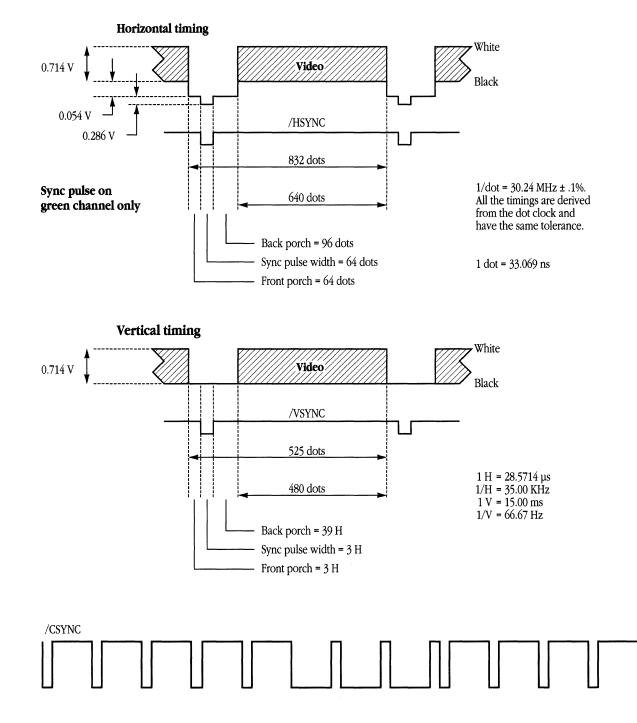

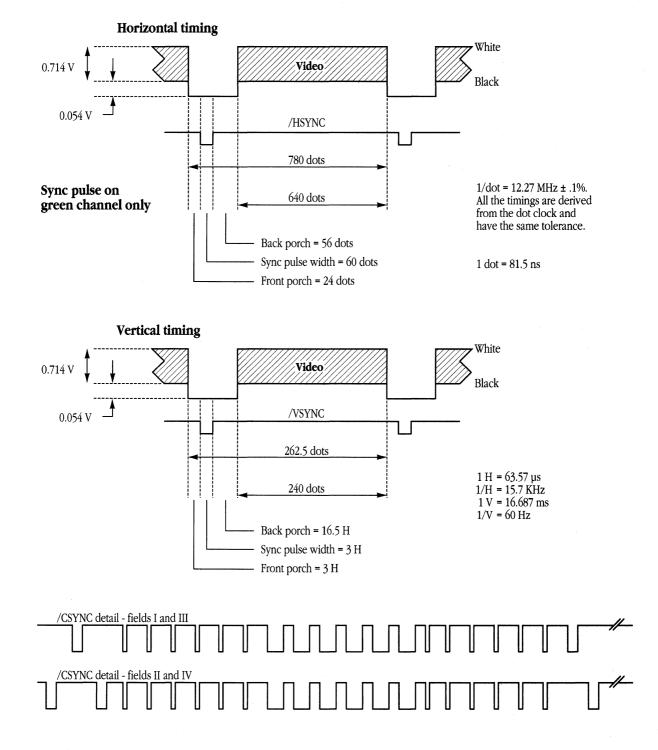

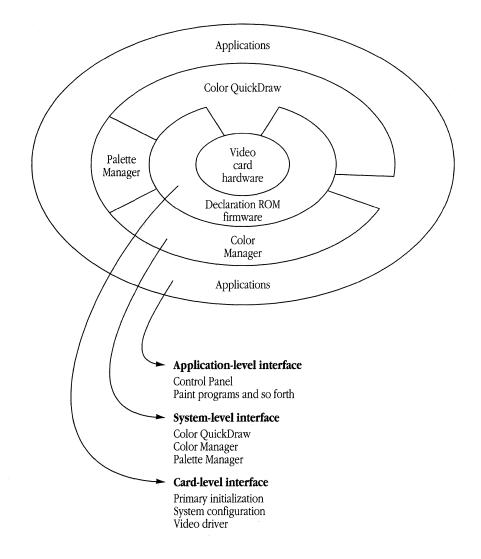

Video card overview / 246 Functional operation / 247 Processor-to-video card interface / 248 Timing generation / 248 Frame Buffer Controller / 248 Video RAM / 249 Color look-up table / 252 Horizontal and vertical scan timing / 252 Declaration ROM operation / 255 Configuration data / 255 The driver / 256 The primary initialization code / 257 Firmware interfaces / 257 Card connectors / 259 Video connector / 259 External-signal connector / 260

## Part II The Processor-Direct Slot Expansion Interface / 261

About Part II / 262

#### 12 Overview of Macintosh PDS Computers / 265

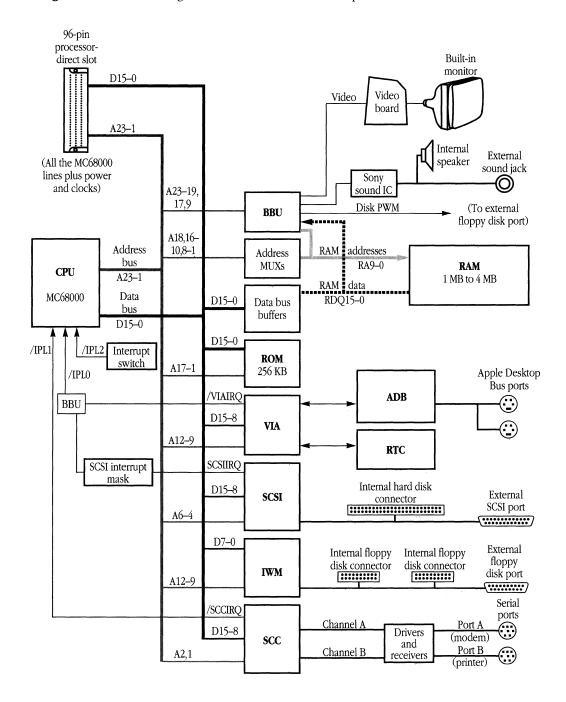

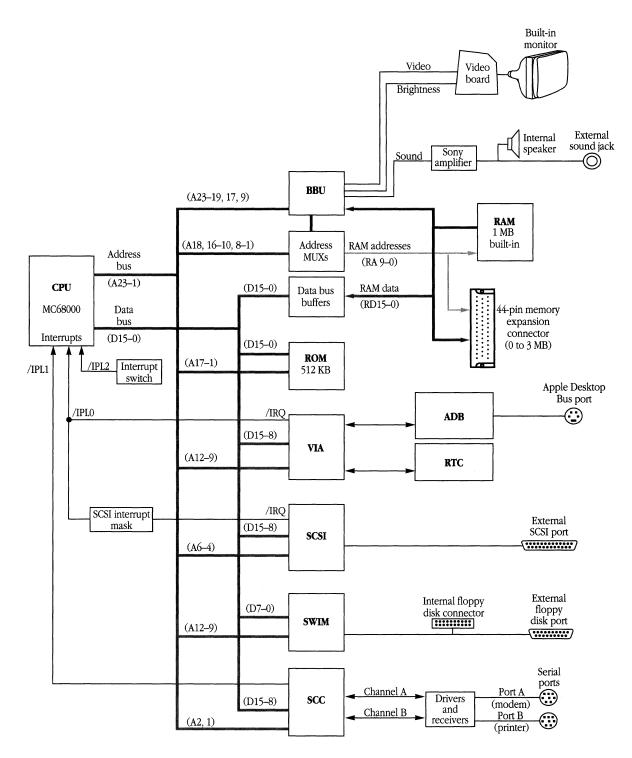

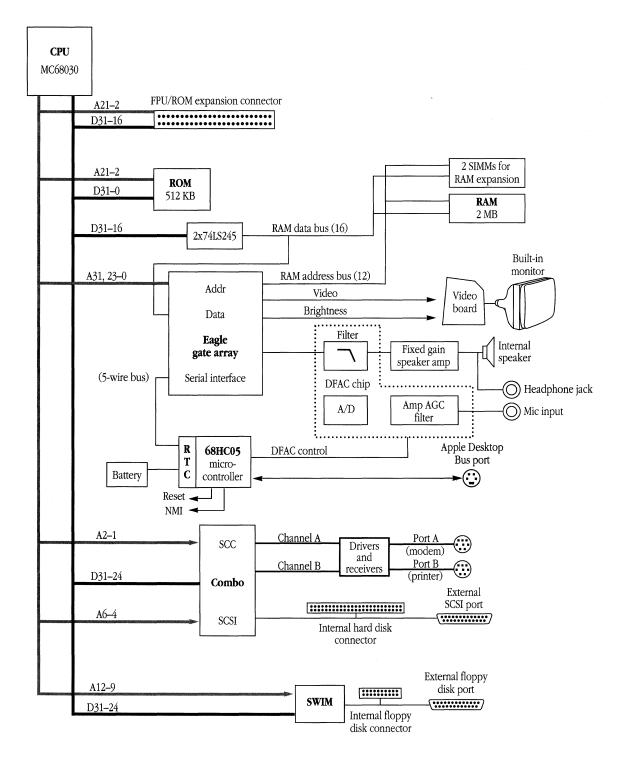

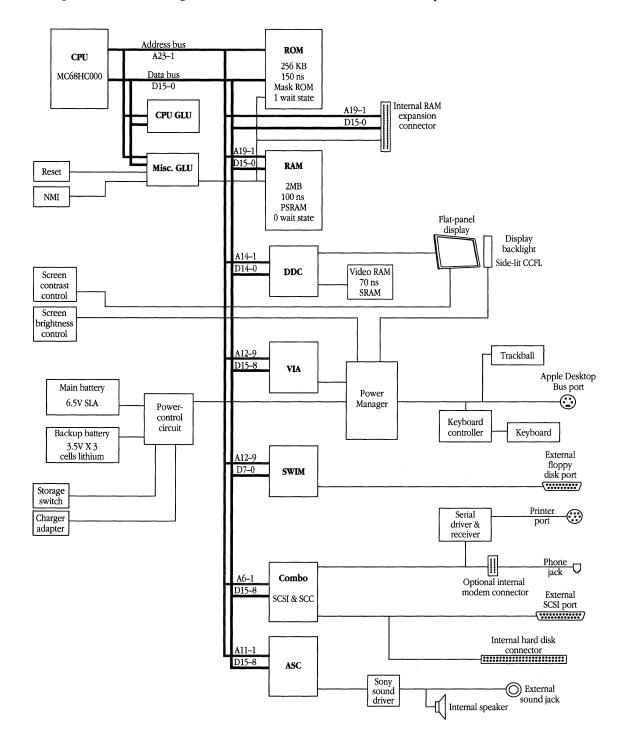

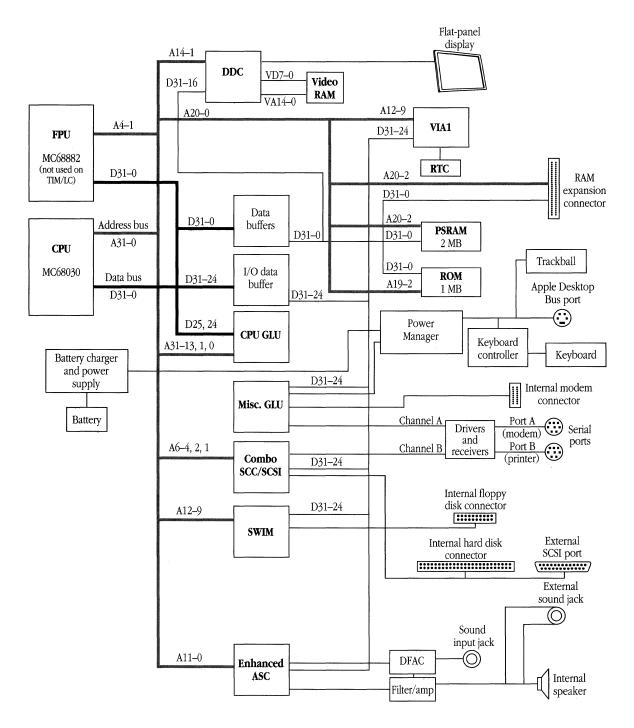

Major features / 266 Hardware architecture / 268 RAM / 275 ROM / 276 Device I/O / 276 PDS expansion interface / 276 The 68000 Direct Slot / 277 The 68020 Direct Slot / 277 The 68030 Direct Slot / 278 The 68040 Direct Slot / 279 Additional support for expansion / 279

### 13 Electrical Design Guide for 68000 Direct Slot Expansion Cards / 281

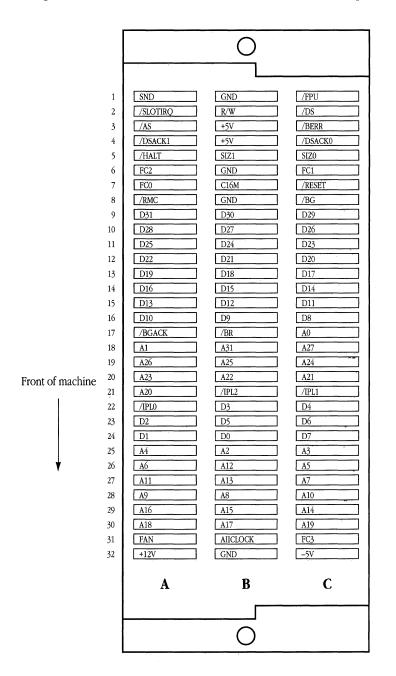

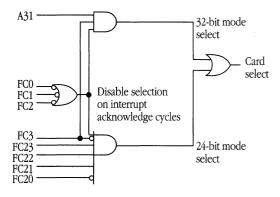

68000 Direct Slot expansion for the Macintosh SE / 282 Electrical description of the Macintosh SE expansion connector / 282 Functional description of the MC68000 signals in the Macintosh SE / 288

Accessing the Macintosh SE electronics from an expansion card / 290 Accessing I/O devices from an expansion card / 290

Accessing RAM from an expansion card / 291

Deviating from the normal RAM access method / 294

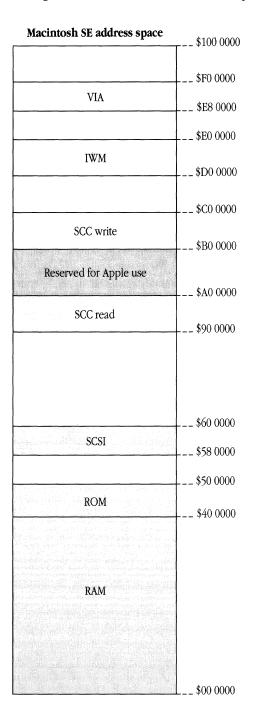

Available Macintosh SE address space / 296

Power consumption guidelines for Macintosh SE PDS expansion cards / 298

68000 Direct Slot expansion for the Macintosh Portable / 299 Electrical description of the Macintosh Portable expansion connector / 299

Functional description of the MC68HC000 signals in the Macintosh Portable / 301

Power consumption guidelines for Macintosh Portable PDS expansion cards / 302

xii

## 14 Electrical Design Guide for 68020 Direct Slot Expansion Cards / 303

68020 Direct Slot expansion for the Macintosh LC / 304

Electrical description of the expansion connector / 304

Load/drive limits of the PDS expansion connector signals for the Macintosh LC /  $\,307$

Electrical design guidelines for the Macintosh LC 68020 Direct Slot expansion card  $\,/\,$  310

Address decode and memory mapping / 310

Addressing guidelines / 311

Electrical design considerations / 311

Accessing I/O and memory devices from the Macintosh LC expansion card  $\,/\,$  312

Power consumption guidelines for Macintosh LC PDS expansion cards / 313

### 15 Electrical Design Guide for 68030 Direct Slot Expansion Cards / 315

68030 Direct Slot expansion / 316

68030 Direct Slot expansion card compatibility issues / 316 Electrical description of the Macintosh SE/30 and the Macintosh IIsi 68030 Direct Slot / 317

Electrical description of the Macintosh IIfx 68030 Direct Slot / 327 Functional description of the MC68030 signals / 335

Macintosh SE/30 and Macintosh IIsi 68030 Direct Slot machinespecific signals  $\ / \ 338$

Machine-specific signals for the Macintosh IIfx 68030 Direct Slot / 339

Electrical design guidelines for Macintosh SE/30 and Macintosh IIsi PDS expansion cards / 340

Memory and I/O access from a Macintosh SE/30 expansion card / 340

Memory and I/O access from Macintosh IIsi expansion cards / 343

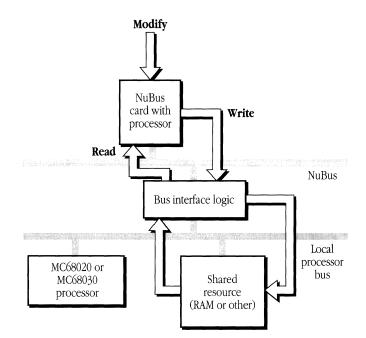

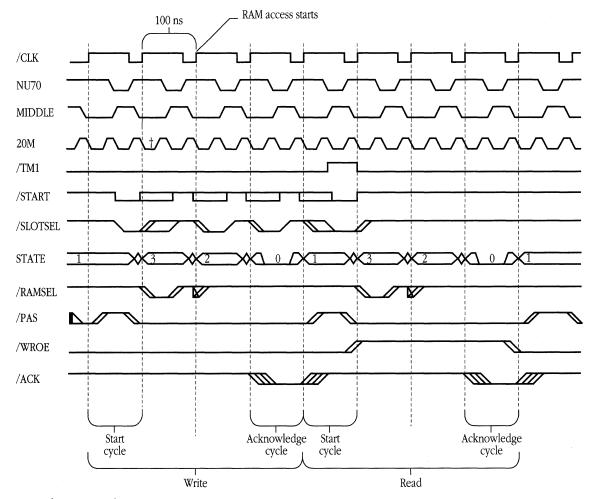

RAM access from a PDS expansion card in the Macintosh IIsi / 344

Pseudoslot design guidelines for Macintosh SE/30 and Macintosh IIsi expansion cards  $/\ 349$

Interrupt handling for the Macintosh SE/30 and Macintosh IIsi 68030 Direct Slot / 351

Design hints for Macintosh SE/30 and Macintosh IIsi expansion cards  $/\ 352$

Power consumption guidelines for Macintosh SE/30 and Macintosh IIsi PDS expansion cards  $/\ 353$

Macintosh IIfx expansion card design / 354

Pseudoslot design guidelines for Macintosh IIfx PDS expansion cards / 355

Memory cycle termination in the Macintosh IIfx / 355

Interrupt handling for the Macintosh IIfx 68030 Direct Slot / 356 Bus master priority scheme for the Macintosh IIfx / 356

Effect of Macintosh IIfx clock speeds on PDS expansion card design  $/\ 357$

Using the Macintosh IIfx cache memory / 358

Additional design hints / 358

Power consumption guidelines for Macintosh IIfx PDS expansion cards  $/\ 359$

Macintosh IIsi PDS adapter card / 359

Macintosh IIsi adapter card cache signals / 361 Power consumption guidelines for the Macintosh IIsi adapter card / 362

### 16 Electrical Design Guide for 68040 Direct Slot Expansion Cards / 363

68040 Direct Slot expansion / 364

Electrical description of the 68040 Direct Slot / 364 Design considerations for 68040 Direct Slot expansion cards / 372

Bus master priority scheme / 373

Memory and I/O access for expansion cards / 374

Pseudoslot design guidelines for PDS expansion cards / 376

Timing considerations / 377

68040 Direct Slot interrupt handling / 377

Cache management / 379

Cache management by ROM / 379

Cache management by applications / 380

Design hints for PDS expansion cards in Macintosh Quadra-family computers / 380

Power consumption guidelines for 68040 Direct Slot expansion cards / 381

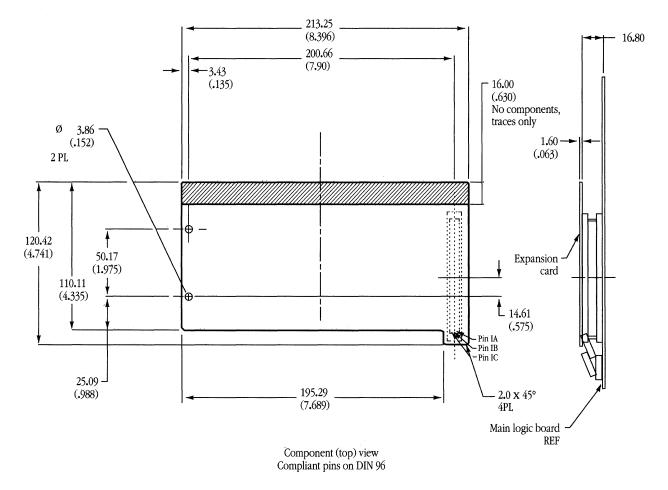

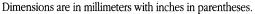

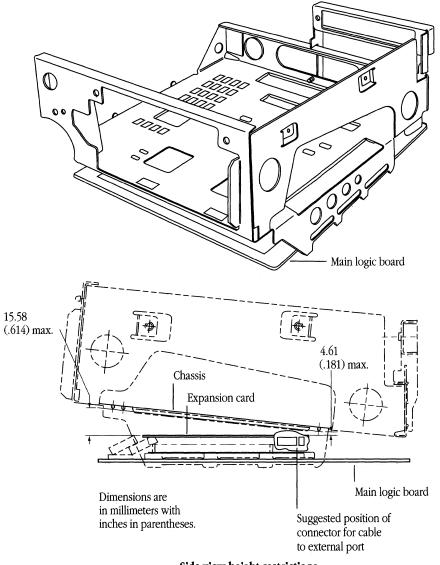

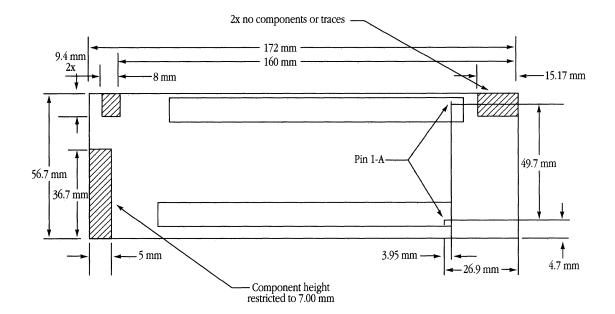

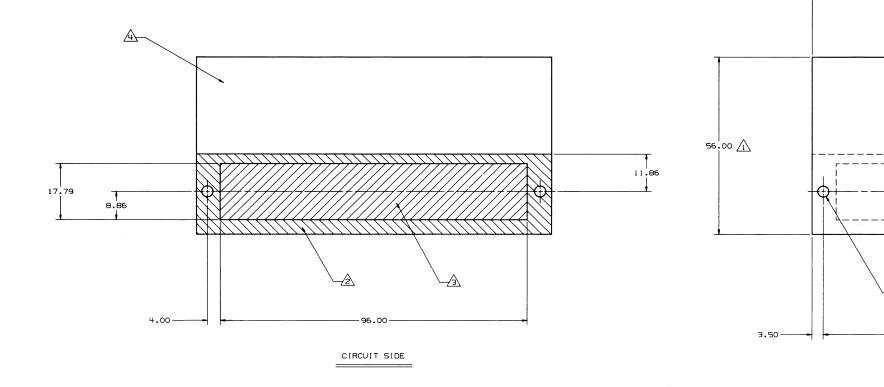

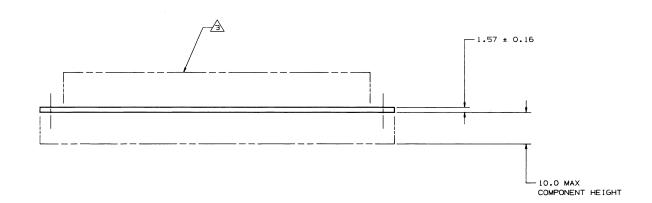

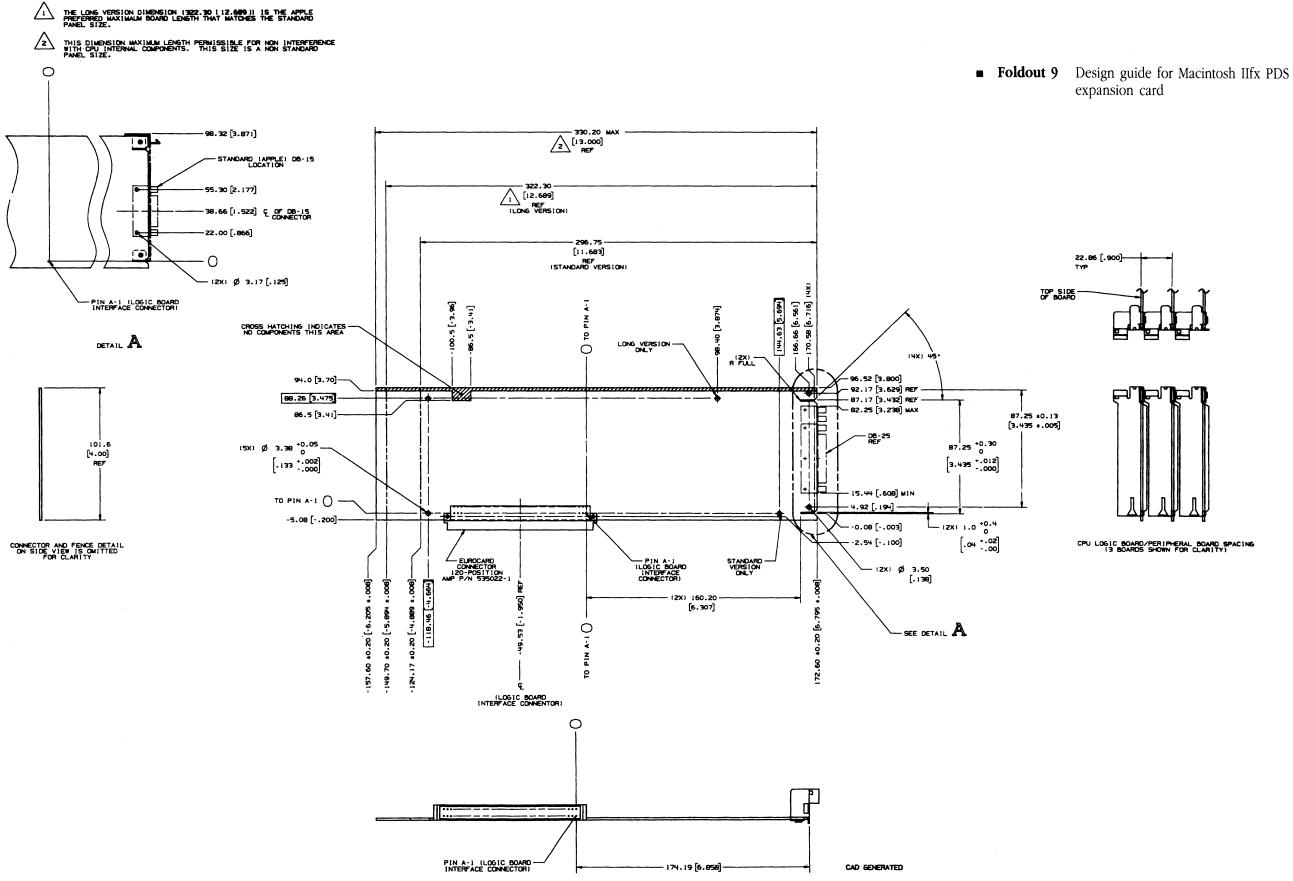

## 17 Physical Design Guide for Macintosh PDS Expansion Cards / 383

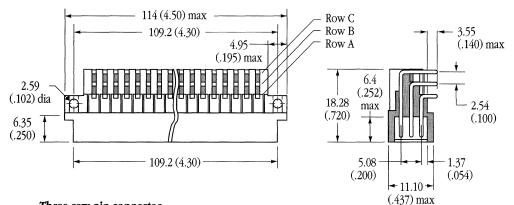

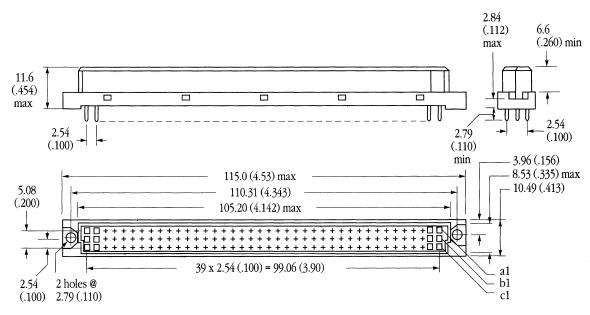

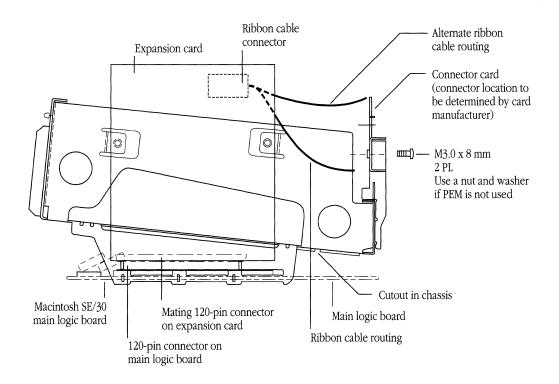

Physical guidelines for Macintosh SE expansion cards / 384 The 68000 Direct Slot 96-pin connector for the Macintosh SE / 386 External connections for the Macintosh SE / 389 Physical guidelines for Macintosh Portable expansion cards / 392 Physical guidelines for Macintosh LC expansion cards / 395 Macintosh LC external access opening / 401 Expansion card installation for the Macintosh LC / 401 Physical guidelines for Macintosh SE/30 expansion cards / 401 The 68030 Direct Slot 120-pin connector for the Macintosh SE/30 / 408 External connection for a Macintosh SE/30 expansion card / 410 Physical guidelines for Macintosh IIfx PDS expansion cards / 412 Physical guidelines for Macintosh IIsi Direct Slot expansion cards / 413 Physical implementation of the Macintosh IIsi 68030 Direct Slot adapter kit / 413 External connections for the Macintosh IIsi PDS expansion card / 414 Design considerations for Macintosh IIsi PDS expansion cards / 415 Macintosh IIsi adapter cards / 415 Physical guidelines for 68040 Direct Slot expansion cards / 417

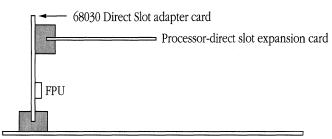

#### 18 Processor-Direct Slot Design Example / 419

Disk controller overview / 420 System configuration / 420 Interface card block diagram / 421 Floppy disk controller logic / 423 Macintosh SE interface logic / 423 Programmed I/O operations / 424 DMA operations / 426 Address allocation / 427

#### Part III Application-Specific Expansion Interfaces / 429 About Part III / 430

## 19 Application-Specific Expansion Interfaces for Macintosh Computers / 431

Major features / 432 Hardware architecture / 434 RAM / 441 ROM / 441 Device I/O / 441

#### 20 RAM Expansion Interface / 443

Macintosh Portable RAM expansion / 444

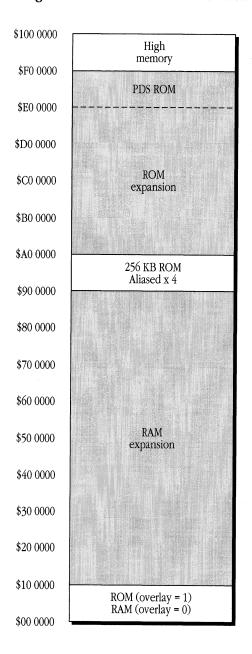

Macintosh Portable RAM expansion address space / 444

RAM expansion cards for the Macintosh Portable / 447

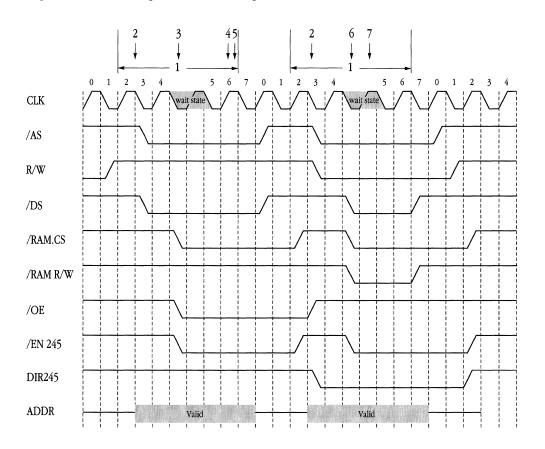

RAM expansion cards for the backlit Macintosh Portable / 450 RAM expansion-slot timing for the backlit Macintosh

Portable / 451

Design considerations for RAM expansion in the backlit Macintosh Portable / 453

Macintosh Classic RAM expansion / 453

Macintosh Classic RAM expansion address space / 453

Electrical description of the RAM expansion cards for the Macintosh Classic / 454

Physical design guide for a Macintosh Classic RAM expansion card / 457

RAM expansion for the PowerBook 140 and PowerBook 170 / 459 Expansion connector signals for the PowerBook 140 and PowerBook 170 / 460

RAM expansion card design guide for the PowerBook 140 and PowerBook 170 / 465

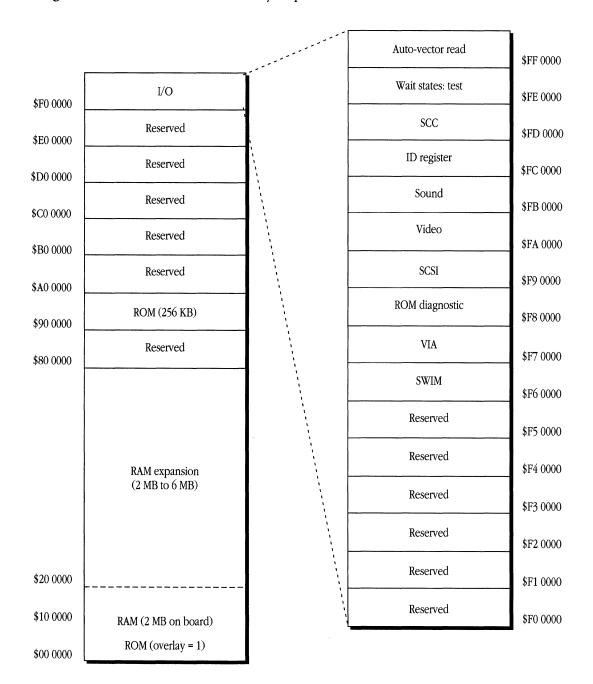

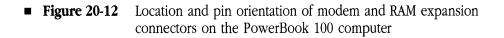

Macintosh PowerBook 100 RAM expansion / 467

RAM address space for the PowerBook 100 / 467

PowerBook 100 RAM expansion connector signals / 469

Design hints for the PowerBook 100 RAM expansion card / 473

PowerBook 100 RAM expansion card design guide / 474

#### 21 ROM Expansion Interface / 475

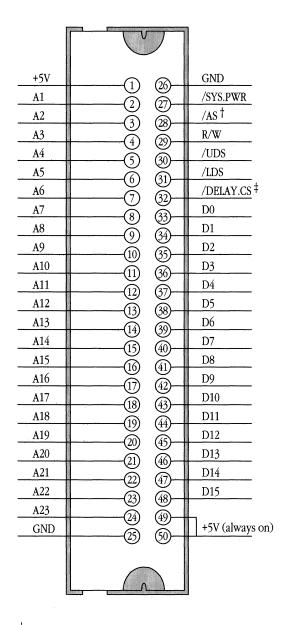

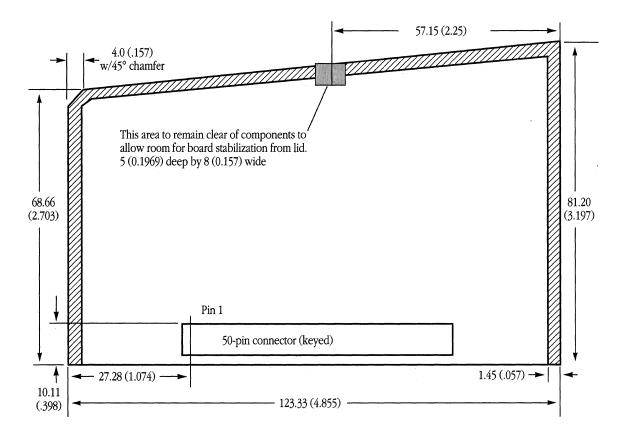

Macintosh Portable ROM expansion / 476 ROM expansion address space in the Macintosh Portable / 476 ROM expansion cards for the Macintosh Portable / 476 Design considerations for ROM expansion in the Macintosh Portable / 479 Macintosh Portable EDisks (electronic disks) / 480 The EDisk driver for the Macintosh Portable / 481 Data checksumming / 481 EDisk driver operation / 482 EDisk header format / 482 FPU/ROM expansion for the Macintosh Classic II computer / 484 Electrical description of the Macintosh Classic II FPU/ROM expansion slot / 485 ROM expansion address space in the Macintosh Classic II computer / 489 Physical design guidelines for the Macintosh Classic II FPU/ROM expansion card / 491 Macintosh Classic II FPU/ROM expansion connector power budget / 492

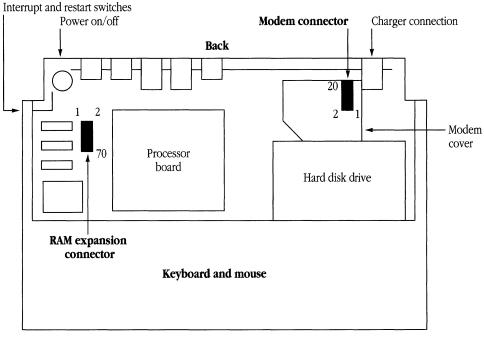

#### 22 Modem Expansion Interface / 493

Macintosh Portable modem card / 494 Modem card hardware interface for the Macintosh Portable / 494 Modem connector electrical interface for the Macintosh Portable / 496 Physical design guide for a Macintosh Portable modem card / 498 Modem power-control interface for the Macintosh Portable / 498 Power-up/power-down timing / 499 Ring detection / 501 Modem card power requirements / 501 Telephone network interface / 501

| Modem expansion cards for the PowerBook-family computers / 502                |

|-------------------------------------------------------------------------------|

| Modem card hardware interface for the PowerBook-family computers / 502        |

| Modem connector electrical interface for the PowerBook-family computers / 505 |

| Physical design guide for the PowerBook-family modem expansion card / 507     |

| Modem power-control interface for the PowerBook family / 509                  |

| Modem operation for the PowerBook family / 510                                |

| Power-up/power-down timing / 510                                              |

| Ring detection / 513                                                          |

| Modem card power requirements / 513                                           |

| Telephone network interface / 513                                             |

| Standards information for reference / 514                                     |

| Compatibility and modulation / 514                                            |

| Transmit carrier frequencies / 514                                            |

| Guard tone frequencies and transmit levels (CCITT only) / 515                 |

| Answer tone frequency / 515                                                   |

| Received signal frequency tolerance / 515                                     |

|                                                                               |

#### 23 Macintosh IIci Cache Memory Expansion / 517

Cache memory expansion overview / 518 How the cache works / 519 Using the cache / 519 Gaining access to the cache card / 520 Electrical description of the cache connector / 521 Electrical design guidelines for the cache card / 527 Mechanical design guidelines for the cache card / 528 Power consumption guidelines / 530

#### A EMI, Heat Dissipation, and Product Safety Guidelines / 531

EMI guidelines for expansion cards / 532

Without external I/O connections / 532

With external I/O connections / 533

Heat dissipation guidelines / 534

Heat dissipation guidelines for NuBus cards / 534

Heat dissipation guidelines for PDS cards / 535

Product safety / 536

- **B** Sample Video Card Firmware / 539

- C Video Card Driver Example / 563

- D PAL Listing for the NuBus Test Card / 591

- E PAL Listing for the SCSI-NuBus Test Card / 601

Glossary / 605

Index / 613

Foldouts / 623

## Figures and tables

#### Preface About This Book / xxxi

Table P-1

Macintosh technical documentation / xxxvi

#### 1 Overview of Macintosh Computers With the NuBus Interface / 13

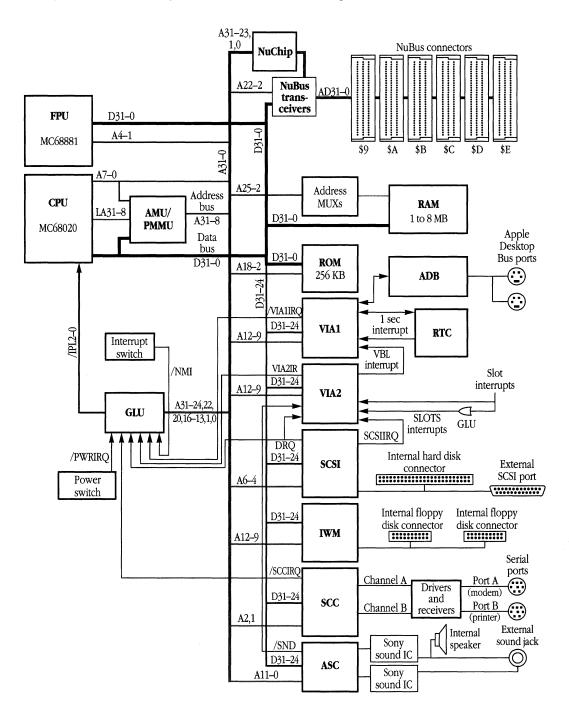

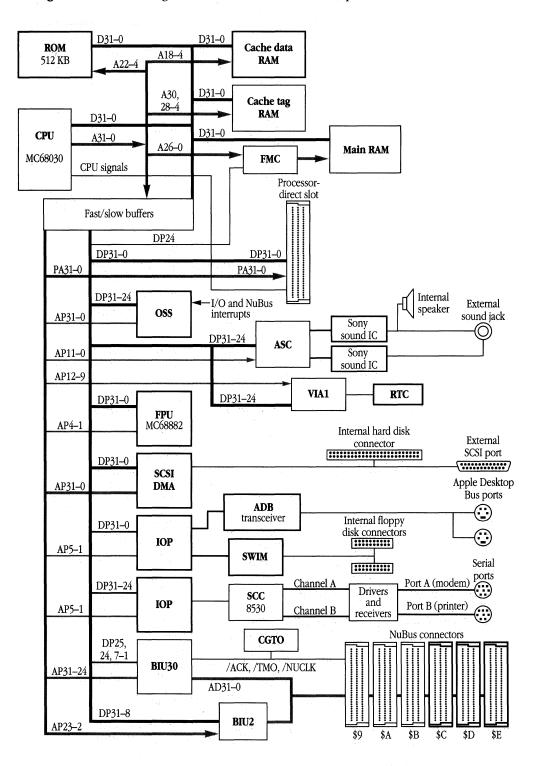

- Figure 1-1 Block diagram of the Macintosh II computer / 21

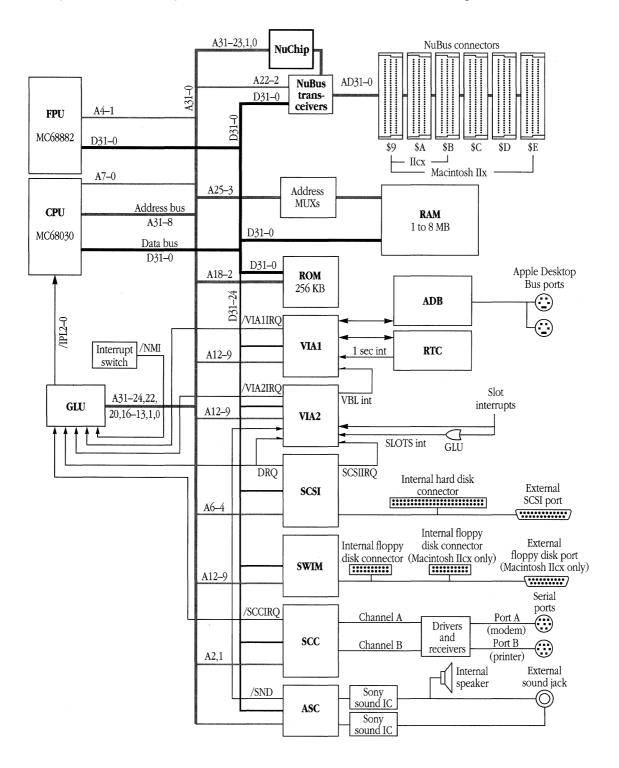

- Figure 1-2 Block diagram of the Macintosh IIx and Macintosh IIcx computers / 22

- Figure 1-3 Block diagram of the Macintosh IIci computer / 23

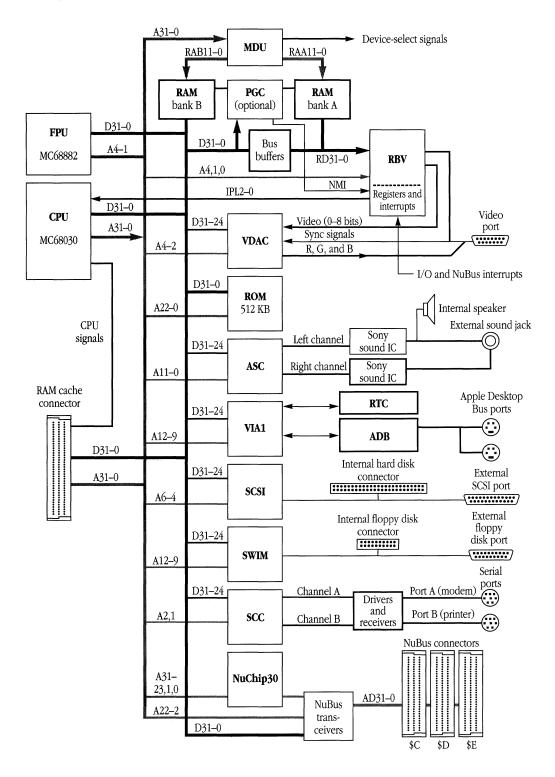

- Figure 1-4 Block diagram of the Macintosh IIfx computer / 24

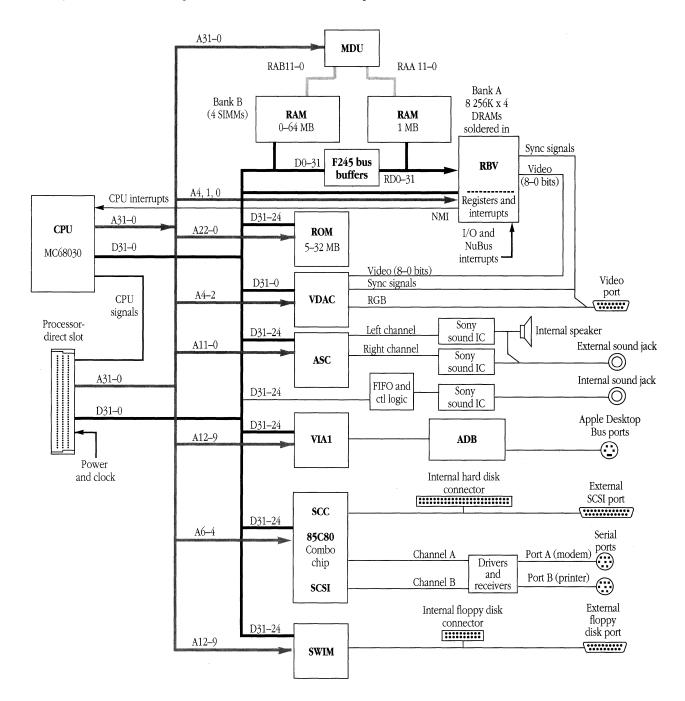

- Figure 1-5 Block diagram of the Macintosh IIsi computer / 25

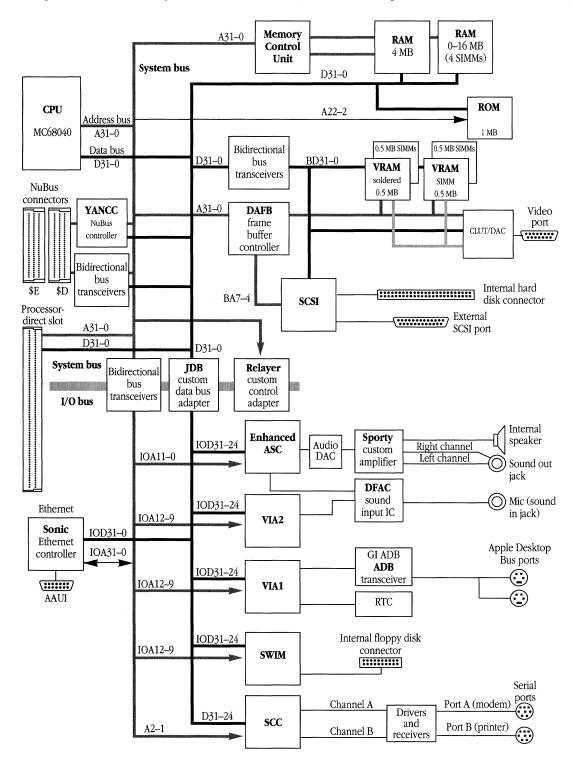

- Figure 1-6 Block diagram of the Macintosh Quadra 700 computer / 26

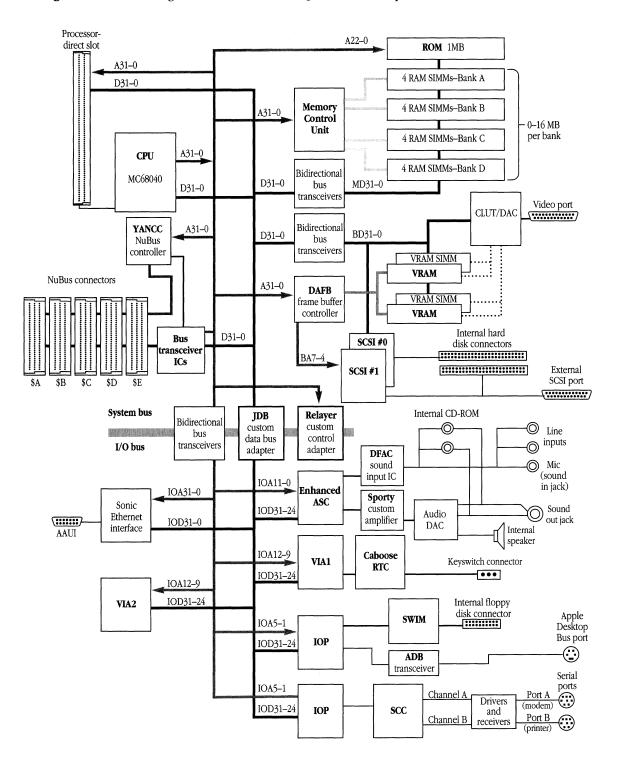

- Figure 1-7 Block diagram of the Macintosh Quadra 900 computer / 27

- Figure 1-8 Bus interface architecture for the Macintosh II, Macintosh IIx, and Macintosh IIcx computers / 33

- Figure 1-9 NuBus-to-processor bus translation / 35

- Table 1-1Major features of Macintosh computers with the NuBus<br/>interface / 14

#### 2 NuBus Overview / 37

- Figure 2-1 Simplified NuBus diagram / 40

- Figure 2-2 NuBus signal timing / 44

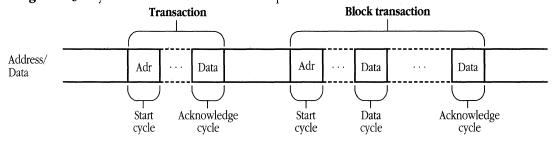

- Figure 2-3 Cycle and transaction relationships / 50

- Table 2-1Design objectives and features / 38

- Table 2-2Signal classifications in the original NuBus<br/>implementation / 42

- Table 2-3Classes of NuBus '90 signals / 43

- Table 2-4NuBus expansion interface terminology / 45

#### 3 NuBus Data Transfer / 51

- Figure 3-1 Words, halfwords, and bytes / 59

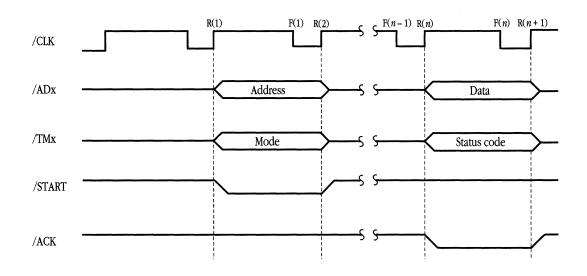

- Figure 3-2 Timing of NuBus read transaction / 61

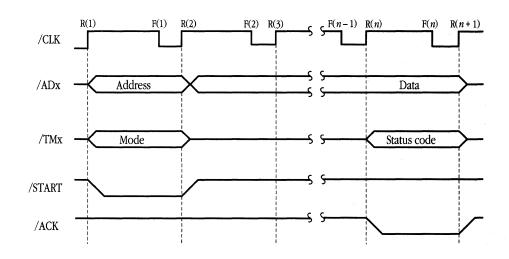

- Figure 3-3 Timing of NuBus write transaction / 62

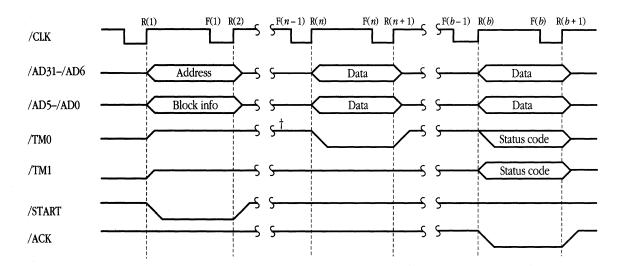

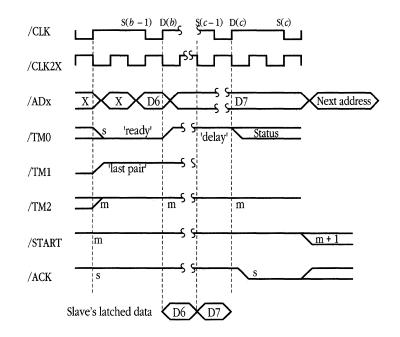

- Figure 3-4 Timing of NuBus 1X block read transaction / 67

- Figure 3-5 Timing of NuBus 1X block write transaction / 69

- Figure 3-6 Timing of NuBus 2X block read transaction / 73

- Figure 3-7 Timing of NuBus 2X block write transaction / 76

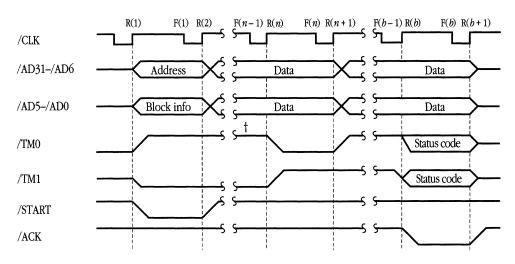

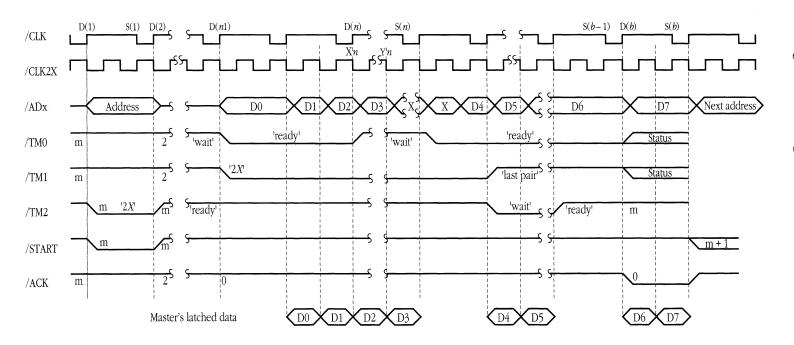

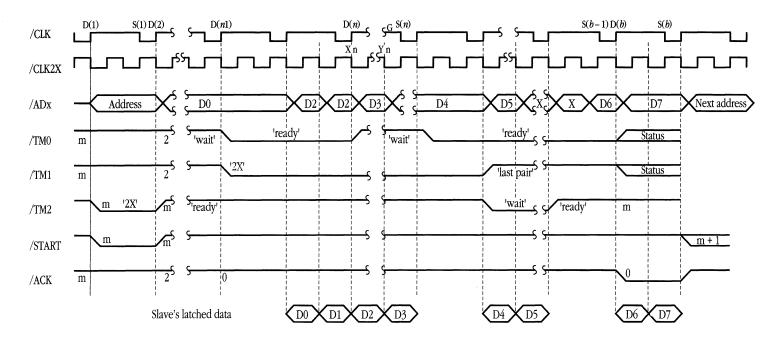

- Figure 3-8 Timing of NuBus 2X block write with delayed status indication / 79

- Table 3-1Transfer mode coding / 57

- Table 3-2Transfer status coding / 63

- Table 3-3Attention cycle coding / 64

- Table 3-4Block size and starting address coding for 1X block<br/>transfers / 66

- Table 3-5Block size and starting address coding for 2X block<br/>transfers / 72

- Table 3-6Cache-coherent transactions / 83

- Table 3-7Cache-coherent transaction encodings / 88

- Table 3-8Cache-coherent master actions / 91

#### 4 NuBus Arbitration / 97

- Figure 4-1 Sample arbitration contest / 99

- Figure 4-2 Typical bus arbitration logic / 100

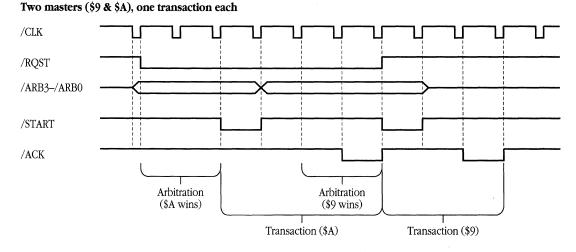

- Figure 4-3 NuBus arbitration and transaction timing, single master and two masters / 102

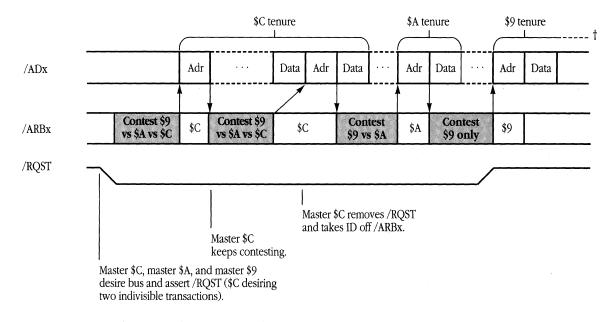

- Figure 4-4 Sample bus lock / 103

- Figure 4-5 Read-modify-write indivisible bus operation / 105

#### 5 NuBus Card Electrical Design Guide / 107

- Figure 5-1 Data-transfer timing diagram / 116

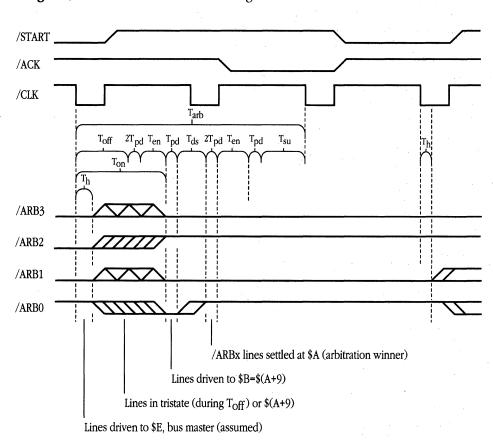

- Figure 5-2 Detailed arbitration timing / 118

- Table 5-1Logical state definitions / 108

- Table 5-2NuBus line drive requirements and load allowances / 109

- Table 5-3Connector pin assignments / 111

- Table 5-4NuBus '90 connector pin assignments / 112

- Table 5-5NuBus '90 signals on the Macintosh Quadra family–NuBus<br/>connectors / 113

| Table 5-6 | Power | supply | specifications | / | 113 |  |

|-----------|-------|--------|----------------|---|-----|--|

|-----------|-------|--------|----------------|---|-----|--|

- Table 5-7Recommended current and capacitance limits for a

- NuBus card / 114

- Table 5-8Data-transfer timing parameters / 117

- Table 5-9Bus arbitration timing parameters/ 118

#### 6 NuBus Card Physical Design Guide / 119

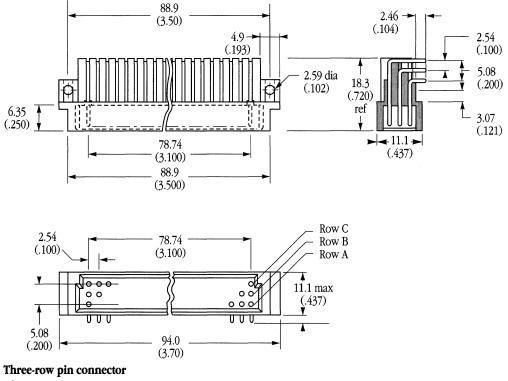

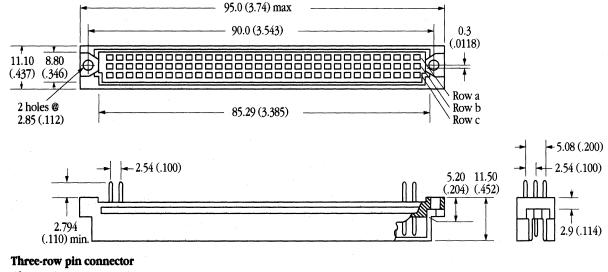

| Figure 6-1 | A 96-pin plug connector for a NuBus expansion card / 12 | 24 |

|------------|---------------------------------------------------------|----|

|            |                                                         |    |

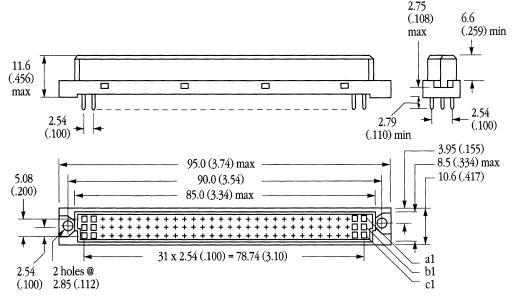

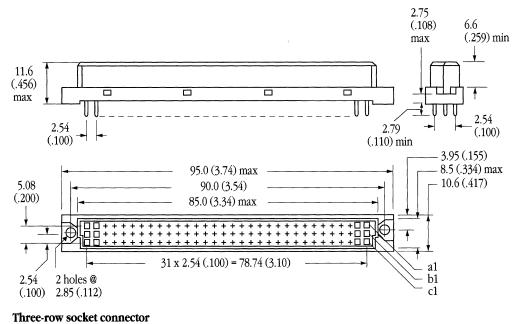

Figure 6-2 A 96-pin socket connector on main logic board / 125

Figure 6-3 Internal connector cabling slot for NuBus expansion card / 126

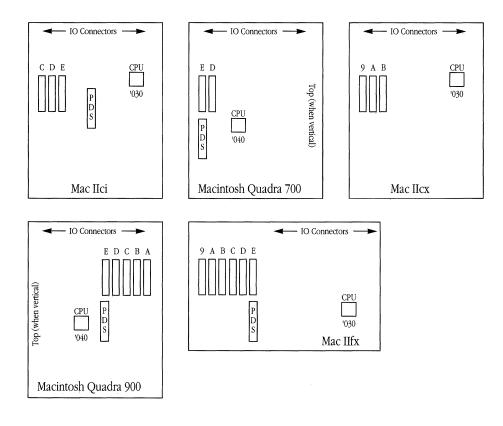

Figure 6-4 NuBus slot ordering on Macintosh IIci, Macintosh Quadra 700, Macintosh IIcx, Macintosh Quadra 900, and Macintosh IIfx computers / 128

Figure 6-5 Installing a NuBus card and adapter on the Macintosh IIsi main logic board / 129

#### 7 NuBus Card Memory Access / 131

| Figure 7-1 | NuBus address space | / | 132 |

|------------|---------------------|---|-----|

|------------|---------------------|---|-----|

- Figure 7-2 Byte-lane mapping / 138

- Figure 7-3 Effect of byte smearing / 139

- Table 7-1NuBus slot IDs and slot spaces for Macintosh<br/>computers / 133

- Table 7-224-to-32-bit address translations / 134

- Table 7-3NuBus address mapping / 135

- Table 7-4Slot allocations / 136

#### 8 NuBus Card Firmware / 141

| Figure 8-1 | Example of sRsrcType fields for a functional            |

|------------|---------------------------------------------------------|

|            | sResource / 148                                         |

| Figure 8-2 | Example of sRsrcType fields for a board                 |

|            | sResource / 149                                         |

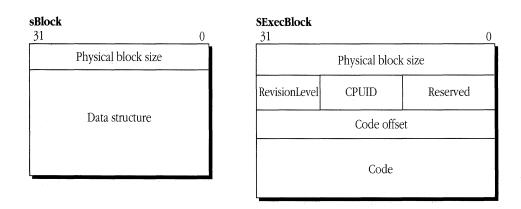

| Figure 8-3 | Formats of sBlock and SExecBlock data types / 152       |

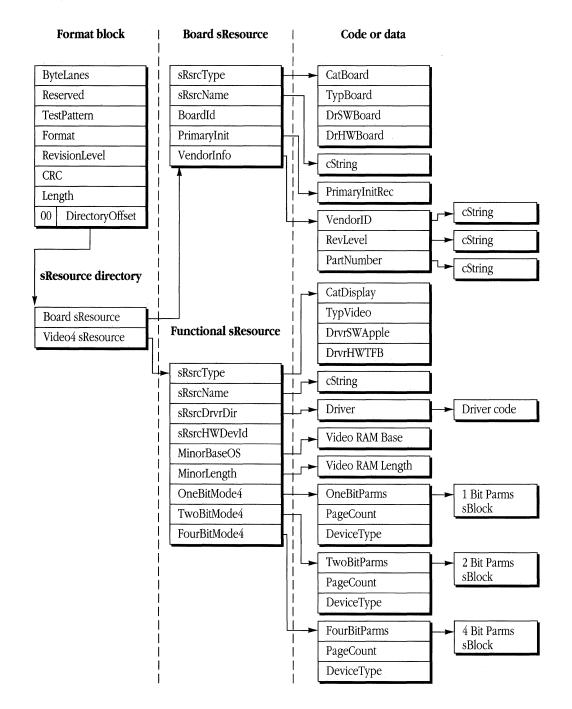

| Figure 8-4 | Firmware structure of the Macintosh II Video Card / 154 |

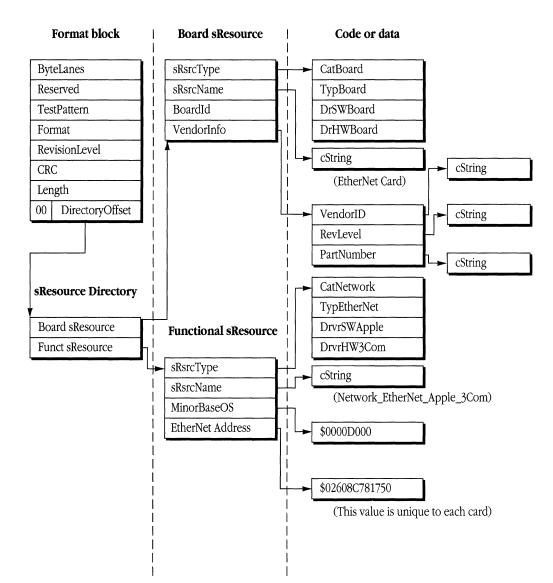

| Figure 8-5 | Firmware structure of the Macintosh II EtherTalk        |

|            | Interface Card / 155                                    |

| Figure 8-6 | Format block structure / 156                            |

| Figure 8-7 | Format block examples / 158                             |

| Figure 8-8 | sResource directory structure / 161                     |

| Figure 8-9 | sResource structure / 162                               |

| Figure 8-10 | The sRsrcType format / 165                     |

|-------------|------------------------------------------------|

| Figure 8-11 | Typical sDriver directory / 167                |

| Figure 8-12 | sMemory resource list for a generic Macintosh  |

|             | Coprocessor Platform card / 173                |

| Figure 8-13 | Typical board sResource / 175                  |

| Figure 8-14 | sPRAMInit record structure / 176               |

| Figure 8-15 | General block-transfer information / 181       |

|             |                                                |

| Table 8-1   | Data types / 152                               |

| Table 8-2   | Possible ByteLanes values / 159                |

| Table 8-3   | Apple-defined sResource ID numbers / 164       |

| Table 8-4   | sDriver directory ID numbers / 167             |

| Table 8-5   | sMemory resource list / 171                    |

| Table 8-6   | Apple-defined board sResource ID numbers / 174 |

| Table 8-7   | VendorInfoID numbers / 178                     |

| Table 8-8   | Block-transfer information fields / 182        |

| Table 8-9   | Apple-defined video sResource ID numbers / 185 |

|             |                                                |

#### 9 NuBus Card Driver Design / 189

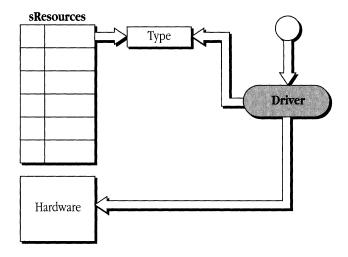

| Figure 9-1 | Card-specific driver / 191                    |

|------------|-----------------------------------------------|

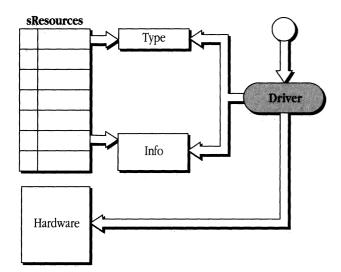

| Figure 9-2 | Card-generic driver / 192                     |

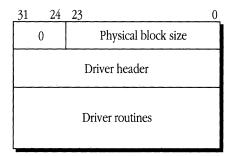

| Figure 9-3 | sDriver record / 193                          |

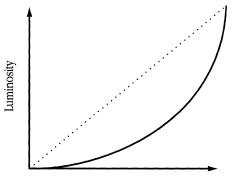

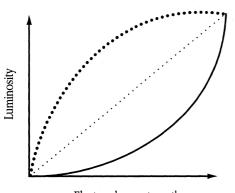

| Figure 9-4 | Color response without gamma correction / 213 |

| Figure 9-5 | Color response with gamma correction / 214    |

|            |                                               |

Table 9-1Video mode list spiD values / 201

Table 9-2Video parameter record / 202

#### 10 NuBus Design Examples / 221

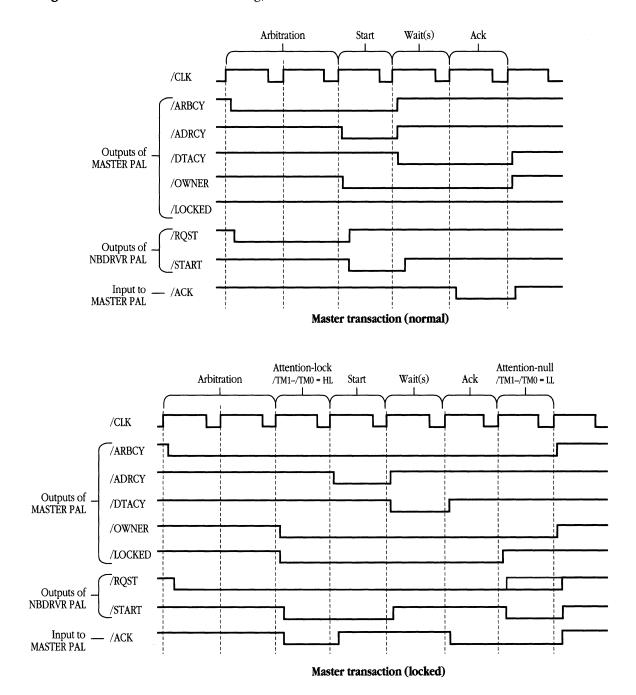

- Figure 10-1 Master transaction timing, normal and locked / 229

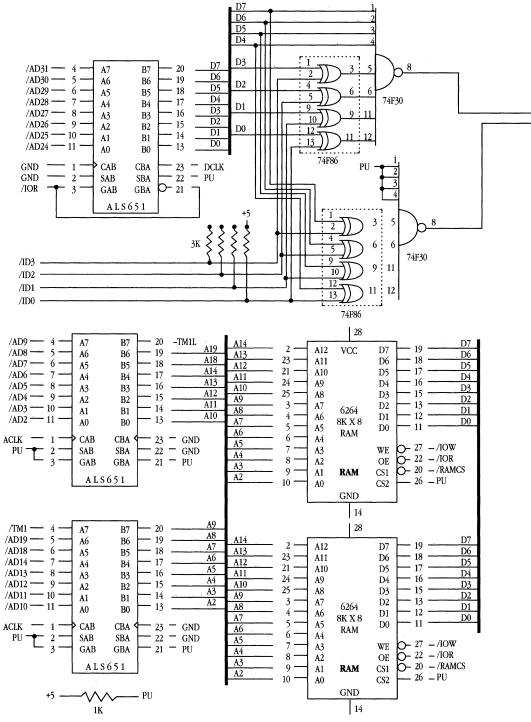

- Figure 10-2 Schematic of SCSI-NuBus Test Card / 232

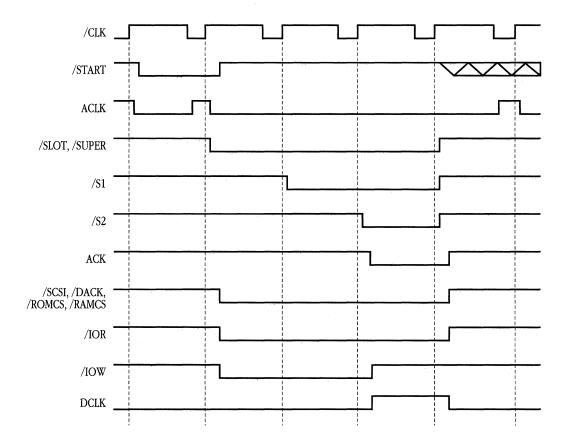

- Figure 10-3 SCSI-NuBus timing diagram / 234

- Figure 10-4 Floppy disk controller block diagram / 238

- Table 10-1Master register interpretation / 223

- Table 10-2Register addresses / 223

- Table 10-3 RAM access signals / 240

- Table 10-4Device select decode addresses / 242

#### 11 The Macintosh II Video Card / 245

| Figure 11-1 | Video card block diagram / 247                          |

|-------------|---------------------------------------------------------|

| Figure 11-2 | Access to video RAM space / 251                         |

| Figure 11-3 | Horizontal and vertical scan timing for high-resolution |

|             | RGB monitor / 253                                       |

| Figure 11-4 | Horizontal and vertical scan timing for the RS-170      |

|             | monitor / 254                                           |

| Figure 11-5 | Firmware levels / 258                                   |

|             |                                                         |

Table 11-1Pin assignments for the video output connector / 259

Table 11-2Pin assignments for the external-signal connector / 260

#### 12 Overview of Macintosh PDS Computers / 265

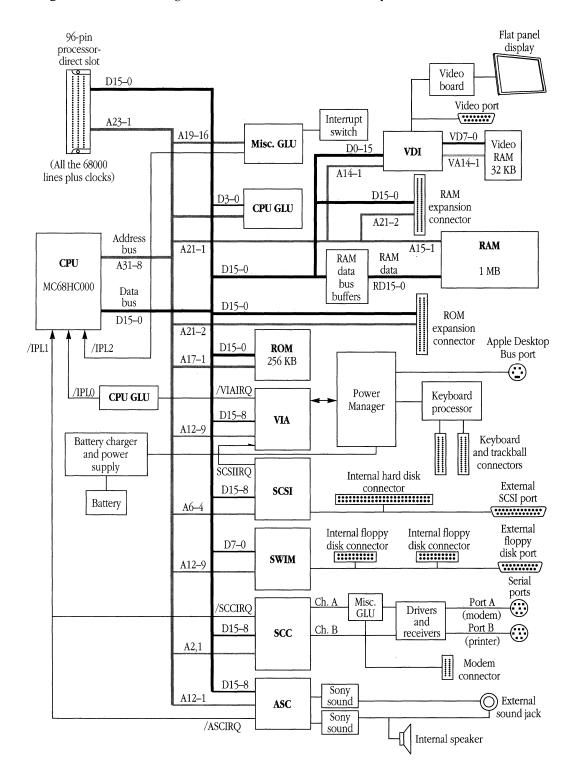

| Figure 12-1 | Block diagram of the Macintosh SE computer / 271       |

|-------------|--------------------------------------------------------|

| Figure 12-2 | Block diagram of the Macintosh Portable computer / 272 |

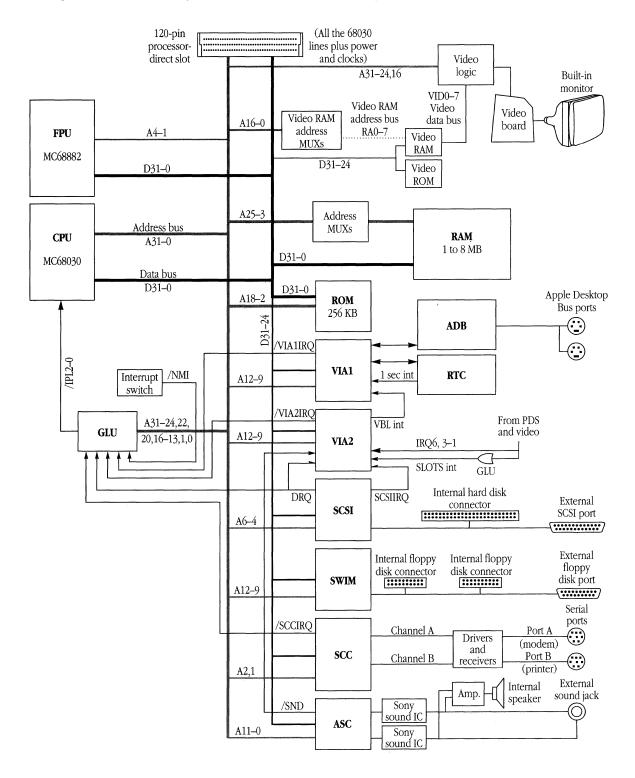

| Figure 12-3 | Block diagram of the Macintosh SE/30 computer / 273    |

| Figure 12-4 | Block diagram of the Macintosh LC computer / 374       |

|             |                                                        |

Table 12-1Major features of Macintosh computers with processor-<br/>direct slots / 266

#### 13 Electrical Design Guide for 68000 Direct Slot Expansion Cards / 281

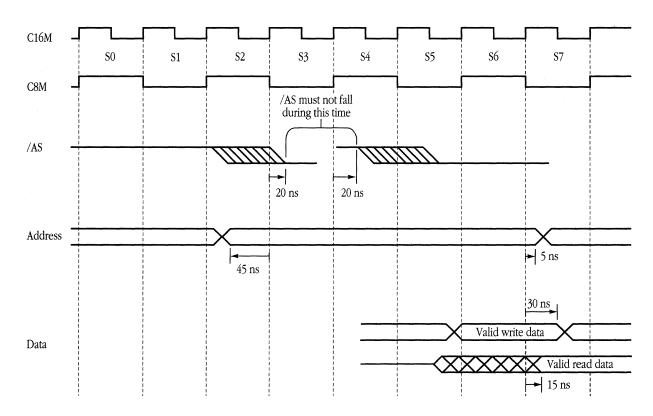

| Figure 13-1 | Macintosh SE 68000 Direct Slot connector pinout / 284                         |

|-------------|-------------------------------------------------------------------------------|

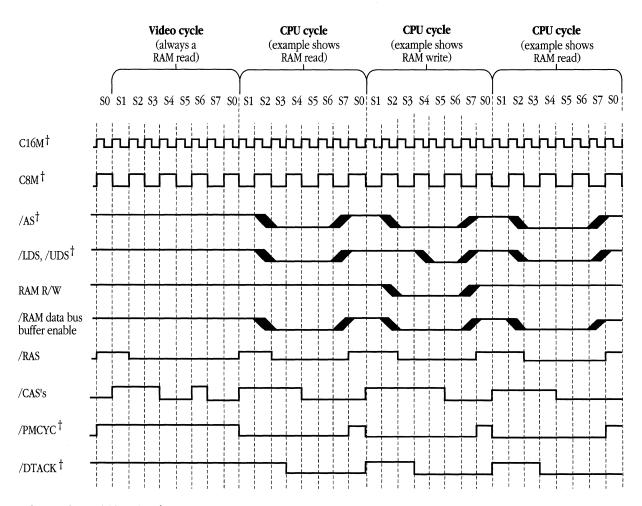

| Figure 13-2 | Timing of video and MC68000 accesses to RAM in the                            |

|             | Macintosh SE / 292                                                            |

| Figure 13-3 | Timing for reading and writing RAM from a Macintosh SE expansion card $/$ 294 |

| Figure 13-4 | Macintosh SE address space / 297                                              |

| Figure 13-5 | Macintosh Portable 68000 Direct Slot connector                                |

|             | pinout / 300                                                                  |

| Table 13-1  | Macintosh SE 68000 Direct Slot signals, loading or driving limits / 285       |

| Table 13-2  | MC68000 signal descriptions / 288                                             |

| Table 13-3  | Macintosh SE 68000 Direct Slot power budget / 298                             |

| Table 13-4  | MC68HC000 signal descriptions / 301                                           |

| Table 13-5  | Macintosh Portable 68000 Direct Slot power budget / 302                       |

|             |                                                                               |

### 14 Electrical Design Guide for 68020 Direct Slot Expansion Cards / 303

| Figure 14-1<br>Figure 14-2 | Macintosh LC 68020 Direct Slot connector pinout / 305<br>Macintosh LC expansion card selection logic / 312 |

|----------------------------|------------------------------------------------------------------------------------------------------------|

| Table 14-1                 | PDS expansion connector signal descriptions for the Macintosh LC / 306                                     |

| Table 14-2                 | Non-processor-direct expansion connector signals for the Macintosh LC / 307                                |

| Table 14-3                 | Macintosh LC 68020 Direct Slot signals, loading or driving limits / 308                                    |

| Table 14-4<br>Table 14-5   | Macintosh LC memory map summary / 310<br>Macintosh LC 68020 Direct Slot power budget / 313                 |

#### 15 Electrical Design Guide for 68030 Direct Slot Expansion Cards / 315

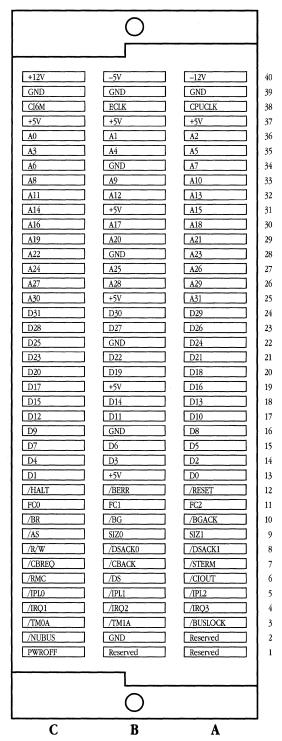

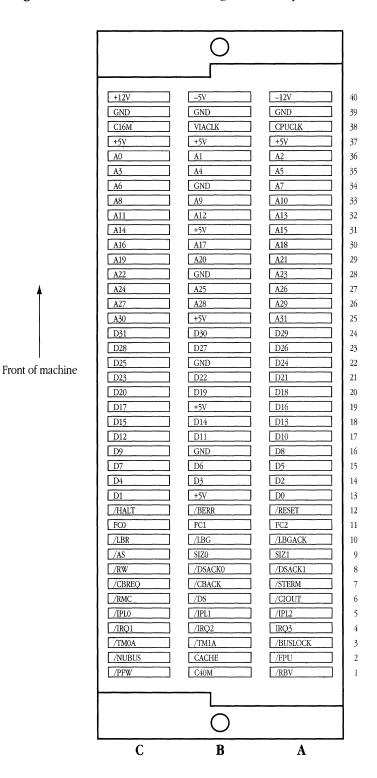

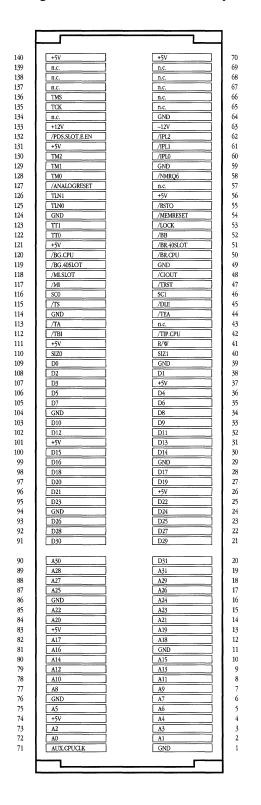

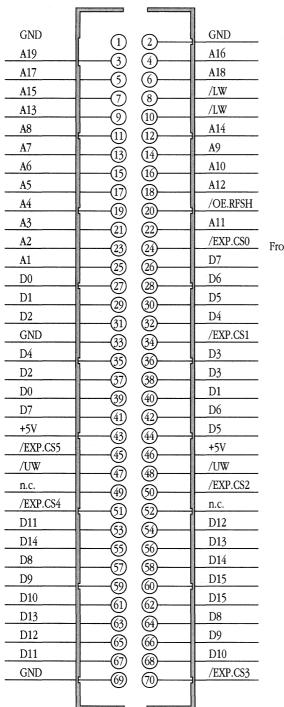

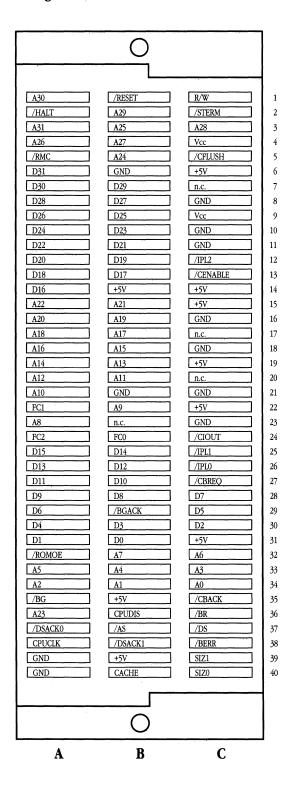

| Figure 15-1 | Macintosh SE/30 and Macintosh IIsi 68030 Direct Slot                                   |

|-------------|----------------------------------------------------------------------------------------|

|             | connector pinout / 318                                                                 |

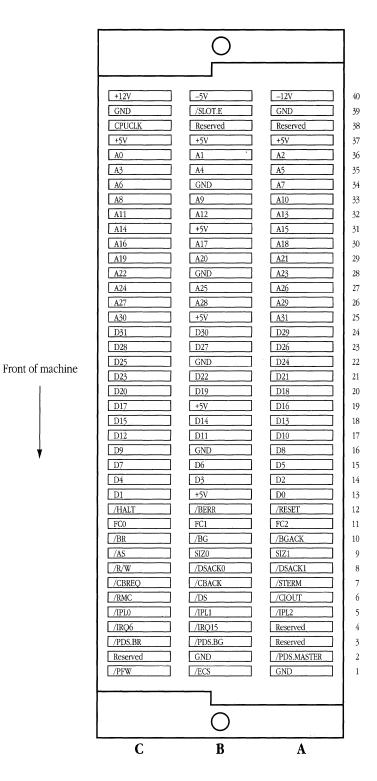

| Figure 15-2 | Macintosh IIfx 68030 Direct Slot expansion connector                                   |

|             | pinout / 329                                                                           |

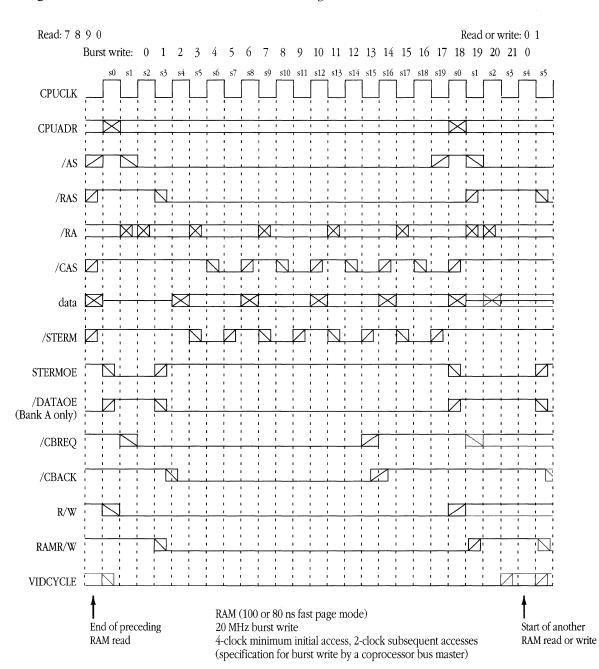

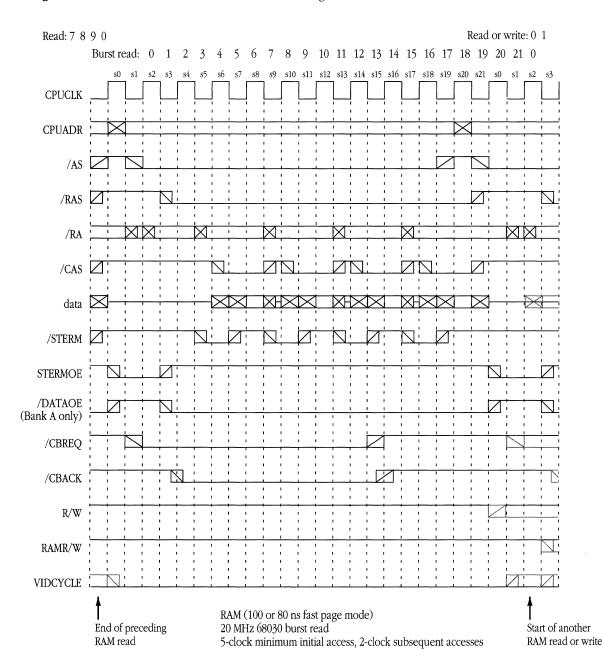

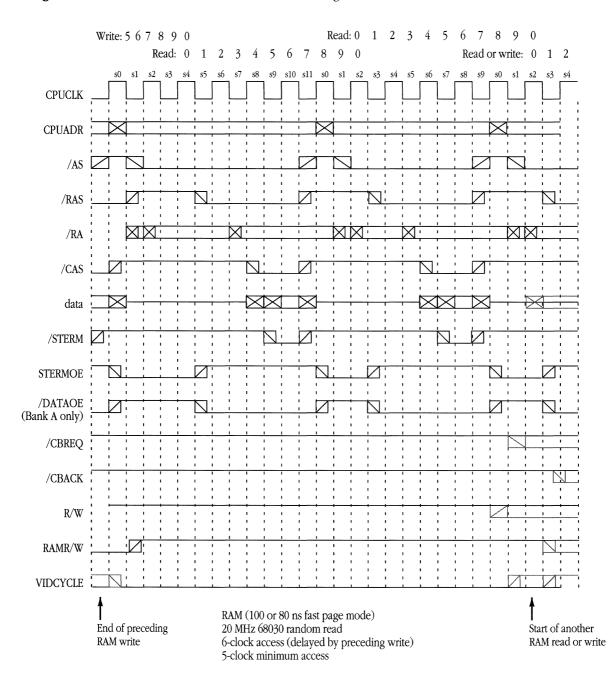

| Figure 15-3 | Macintosh IIsi RAM burst-write timing / 345                                            |

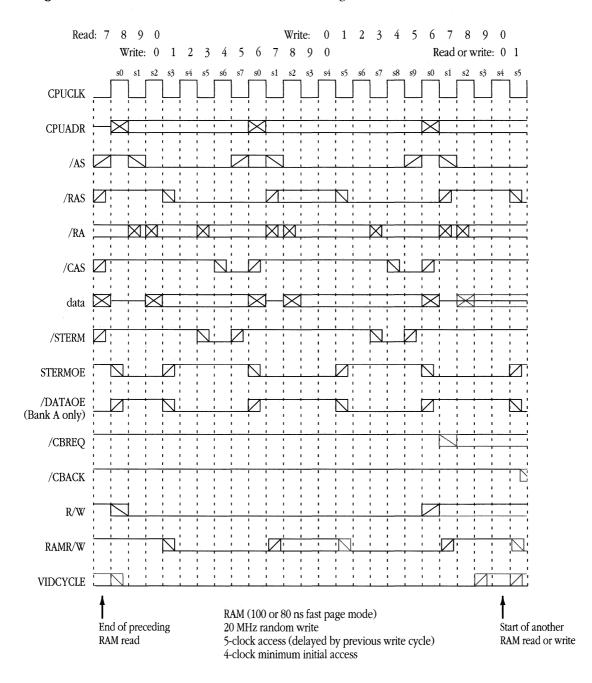

| Figure 15-4 | Macintosh IIsi RAM random-write timing / 346                                           |

| Figure 15-5 | Macintosh IIsi RAM burst-read timing / 347                                             |

| Figure 15-6 | Macintosh IIsi RAM random-read timing / 348                                            |

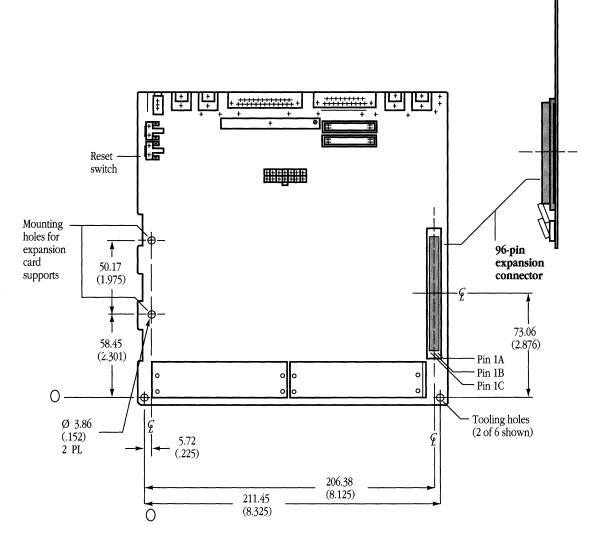

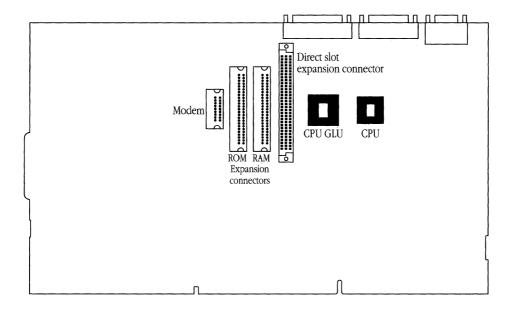

| Figure 15-7 | Macintosh IIsi main logic board expansion                                              |

|             | connector / 360                                                                        |

| Table 15-1  | Macintosh SE/30 and Macintosh IIsi 68030 Direct Slot<br>connector signals / 319        |

| Table 15-2  | Macintosh SE/30 68030 Direct Slot signals, loading or driving limits / 324             |

| Table 15-3  | Macintosh IIsi 68030 Direct Slot signals, loading or driving limits / 326              |

| Table 15-4  | Macintosh IIfx 68030 Direct Slot connector signals / 330                               |

| Table 15-5  | Macintosh IIfx 68030 Direct Slot signals, loading or                                   |

|             | driving limits / 333                                                                   |

| Table 15-6  | 68030 Direct Slot common signals / 336                                                 |

| Table 15-7  | Macintosh SE/30 and Macintosh IIsi 68030 Direct Slot<br>machine-specific signals / 339 |

| Table 15-8  | Macintosh IIfx machine-specific signals on the 68030  |

|-------------|-------------------------------------------------------|

|             | Direct Slot / 340                                     |

| Table 15-9  | Macintosh SE/30 32-bit physical address spaces / 342  |

| Table 15-10 | Macintosh IIsi 32-bit physical address spaces / 344   |

| Table 15-11 | 24-to-32-bit logical address translation map / 350    |

| Table 15-12 | Pseudoslot address ranges for Macintosh SE/30 and     |

|             | Macintosh IIsi expansion cards / 351                  |

| Table 15-13 | Power budget for a Macintosh SE/30 and Macintosh IIsi |

|             | expansion card / 354                                  |

| Table 15-14 | Macintosh IIfx bus master priority scheme / 356       |

| Table 15-15 | Macintosh IIsi custom adapter card signals / 361      |

|             |                                                       |

#### 16 Electrical Design Guide for 68040 Direct Slot Expansion Cards / 363

| Figure 16-1 | 68040 Direct Slot expansion connector pinout / 365         |

|-------------|------------------------------------------------------------|

| Table 16-1  | 68040 Direct Slot connector signals / 366                  |

| Table 16-2  | Restricted 68040 microprocessor signals on the Macintosh   |

|             | Quadra 700 and Macintosh Quadra 900 PDS                    |

|             | connectors / 370                                           |

| Table 16-3  | 68040 Direct Slot signals, loading or driving limits / 371 |

| Table 16-4  | Bus master priority scheme for the Macintosh Quadra-       |

|             | family computers / 374                                     |

| Table 16-5  | Macintosh Quadra 700 and Macintosh Quadra 900 32-bit       |

|             | physical address spaces / 375                              |

| Table 16-6  | Macintosh Quadra 700 and Macintosh Quadra 900 VIA2         |

|             | interrupt lines / 378                                      |

| Table 16-7  | Macintosh Quadra 700 and Macintosh Quadra 900              |

|             | interrupt mapping / 378                                    |

|             |                                                            |

#### 17 Physical Design Guide for Macintosh PDS Expansion Cards / 383

| Figure 17-1                | Macintosh SE expansion card design guide / 384                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------------|

| Figure 17-2<br>Figure 17-3 | An expansion card in the Macintosh SE assembly / 385<br>An expansion card and the Macintosh SE main logic |

| riguic 1/-J                | board / 386                                                                                               |

| Figure 17-4                | A 96-pin plug connector for a Macintosh SE expansion<br>card / 387                                        |

| Figure 17-5                | Macintosh SE connector and mounting supports for an expansion card / 388                                  |

| Figure 17-6                | Detail of 96-pin socket connector used on Macintosh SE main logic board / 389                             |

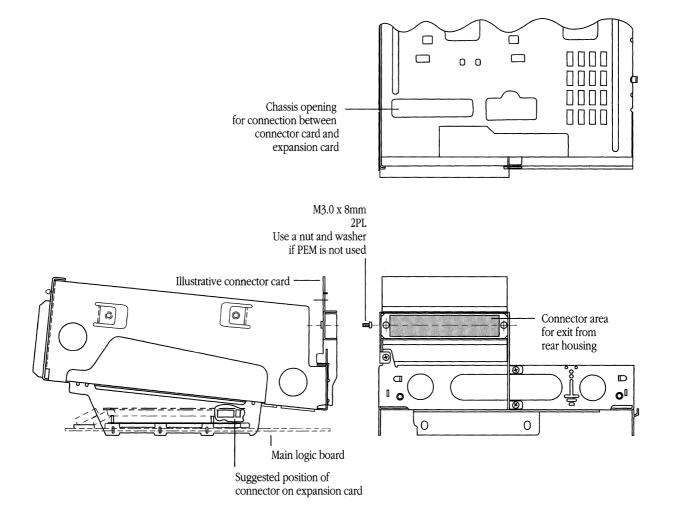

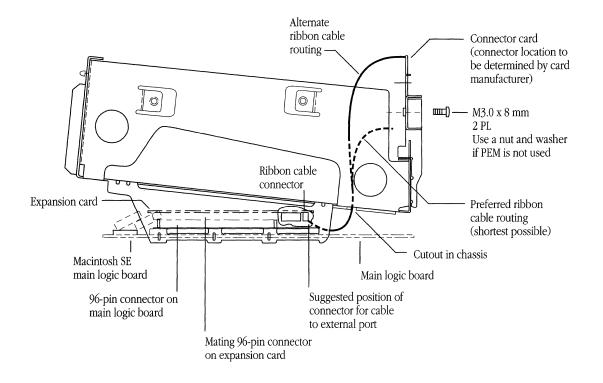

| Figure 17-7  | Connector card mounting on Macintosh SE chassis / 391                        |

|--------------|------------------------------------------------------------------------------|

| Figure 17-8  | Internal expansion cable routing for Macintosh SE / 392                      |

| Figure 17-9  | Expansion connector location on Macintosh Portable                           |

|              | main logic board / 393                                                       |

| Figure 17-10 | The Macintosh Portable 68000 Direct Slot expansion                           |

|              | card / 394                                                                   |

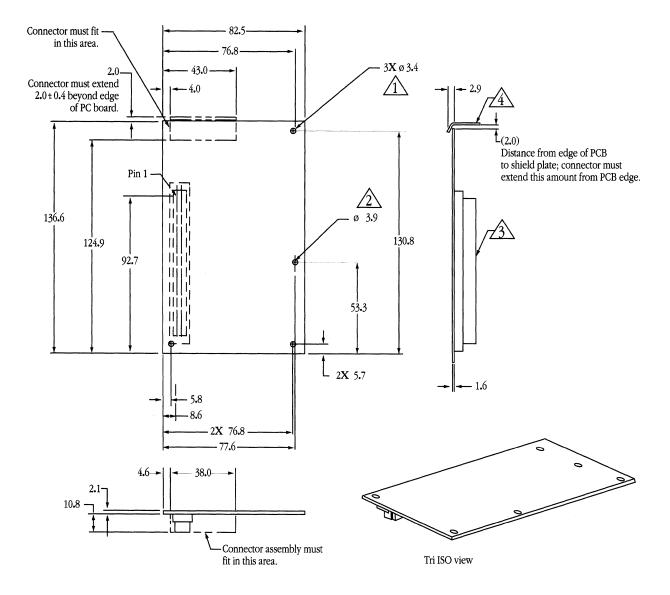

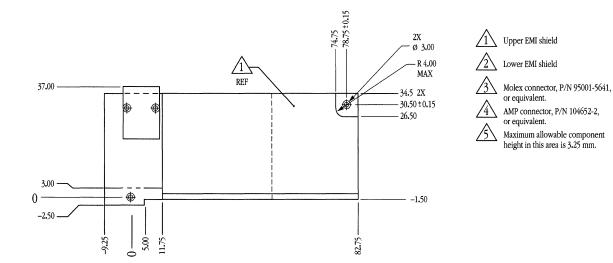

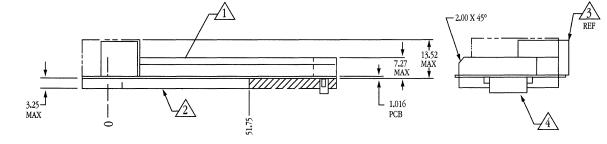

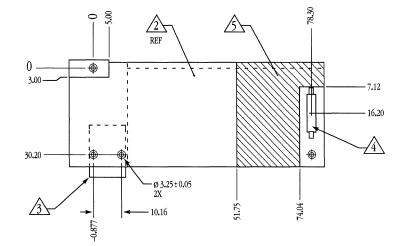

| Figure 17-11 | Macintosh LC expansion card design guide / 396                               |

| Figure 17-12 | Macintosh LC expansion card component location and height restrictions / 397 |

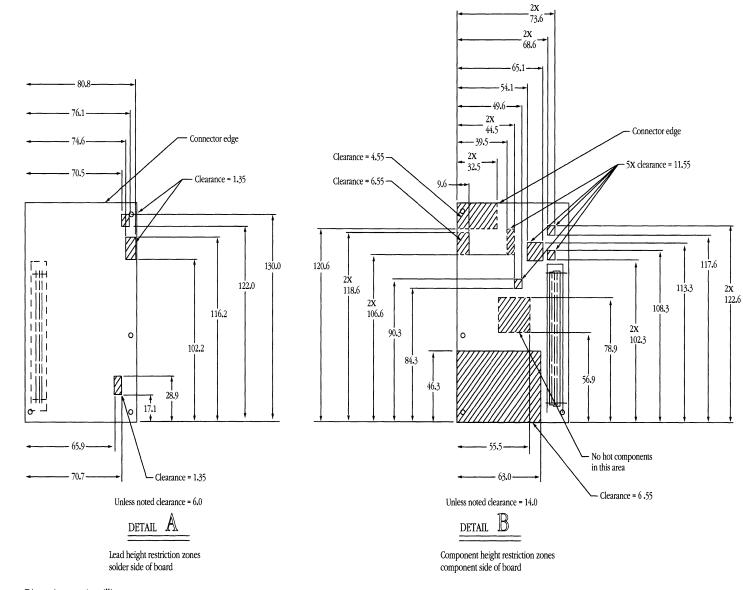

| Figure 17-13 | Design guide for Macintosh LC expansion card shield                          |

| 118010 17 19 | plate / 398                                                                  |

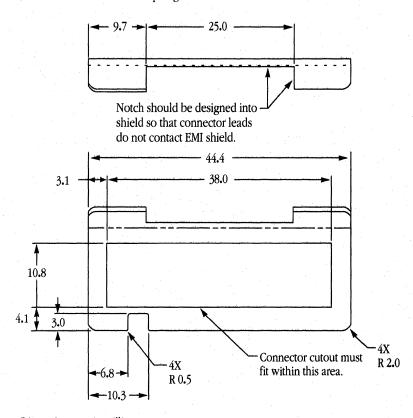

| Figure 17-14 | Positioning the expansion card on the Macintosh LC main                      |

| 0            | logic board / 399                                                            |

| Figure 17-15 | Plastic supports for Macintosh LC expansion cards / 400                      |

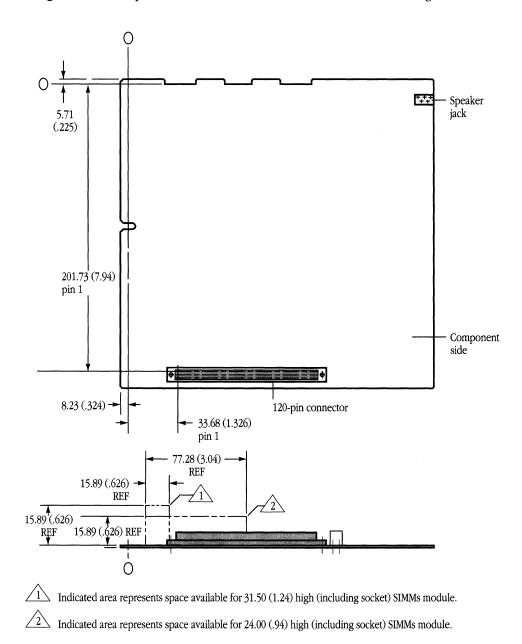

| Figure 17-16 | Smallest allowable Macintosh SE/30 expansion card / 402                      |

| Figure 17-17 | Largest allowable Macintosh SE/30 expansion card / 403                       |

| Figure 17-18 | Largest allowable component heights for a Macintosh                          |

|              | SE/30 expansion card / 404                                                   |

| Figure 17-19 | Expansion connector on the Macintosh SE/30 main logic                        |

|              | board / 405                                                                  |

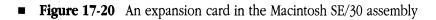

| Figure 17-20 | An expansion card in the Macintosh SE/30 assembly / 406                      |

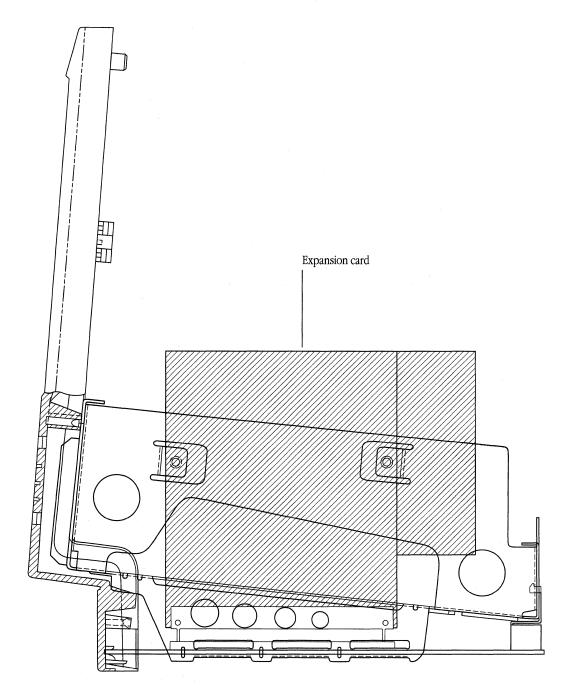

| Figure 17-21 | Orientation of Macintosh SE/30 mounting                                      |

|              | hardware / 407                                                               |

| Figure 17-22 | A 120-pin plug connector for a Macintosh SE/30                               |

|              | expansion card / 408                                                         |

| Figure 17-23 | Detail of 120-pin socket connector used on Macintosh                         |

|              | SE/30 main logic board / 409                                                 |

| Figure 17-24 | Internal expansion cable routing for Macintosh                               |

|              | SE/30 / 411                                                                  |

| Figure 17-25 | Installing a PDS card and adapter on the Macintosh IIsi                      |

|              | main logic board / 414                                                       |

| Figure 17-26 | Macintosh IIsi PDS adapter card outline / 416                                |

| Processor-Di | rect Slot Design Example / 419                                               |

| Figure 18-1  | Floppy disk controller block diagram / 422                                   |

|              |                                                                              |

- Figure 18-2 Disk controller PIO timing / 425

- Table 18-1Bus control signals / 423

18

Table 18-2Device select decode addresses / 427

## 19 Application-Specific Expansion Interfaces for Macintosh Computers / 431

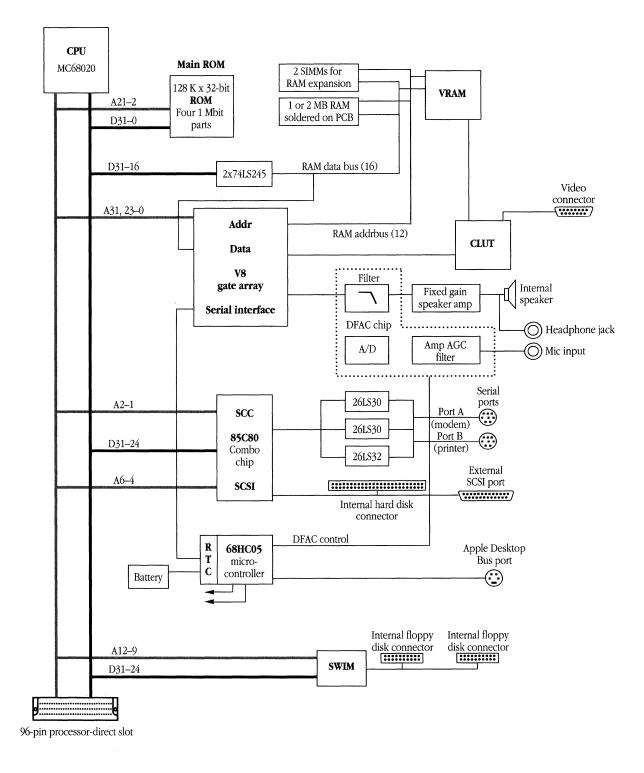

| Figure 19-1 | Block diagram of the Macintosh Classic computer / 437                                       |

|-------------|---------------------------------------------------------------------------------------------|

| Figure 19-2 | Block diagram of the Macintosh Classic II computer / 438                                    |

| Figure 19-3 | Block diagram of the Macintosh PowerBook 100                                                |

|             | computer / 439                                                                              |

| Figure 19-4 | Block diagram of the Macintosh PowerBook 140 and<br>Macintosh PowerBook 170 computers / 440 |

|             |                                                                                             |

Table 19-1Major features of Macintosh computers with application-<br/>specific expansions / 432

## 20 RAM Expansion Interface / 443

| Figure 20-1  | Macintosh Portable memory map / 446                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| Figure 20-2  | Macintosh Portable RAM expansion connector<br>pinout / 448                                                                      |

| Figure 20-3  | Macintosh Portable RAM expansion card design guide / 450                                                                        |

| Figure 20-4  | RAM expansion-slot timing for the backlit Macintosh<br>Portable / 452                                                           |

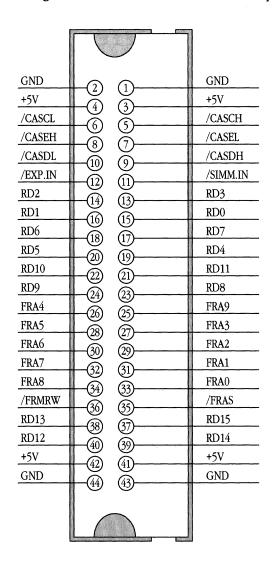

| Figure 20-5  | Macintosh Classic RAM expansion connector pinout / 455                                                                          |

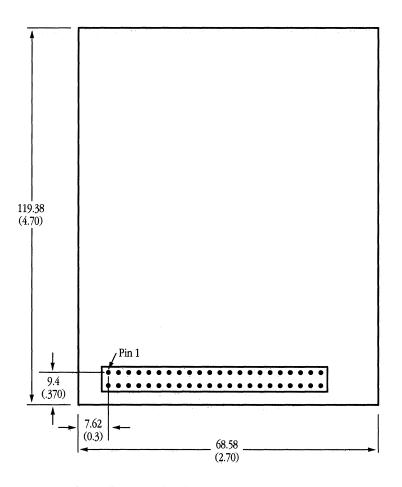

| Figure 20-6  | RAM expansion card design guide for the Macintosh<br>Classic / 458                                                              |

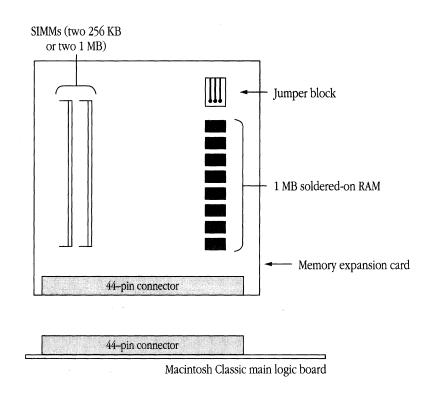

| Figure 20-7  | Macintosh Classic RAM expansion card configuration / 459                                                                        |

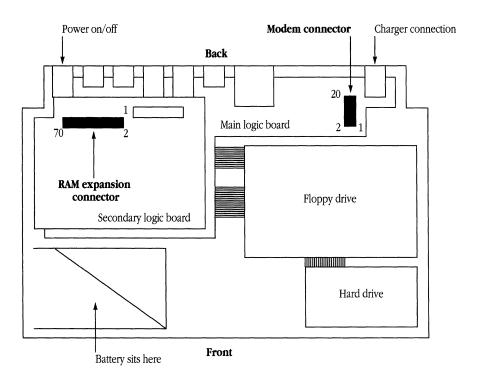

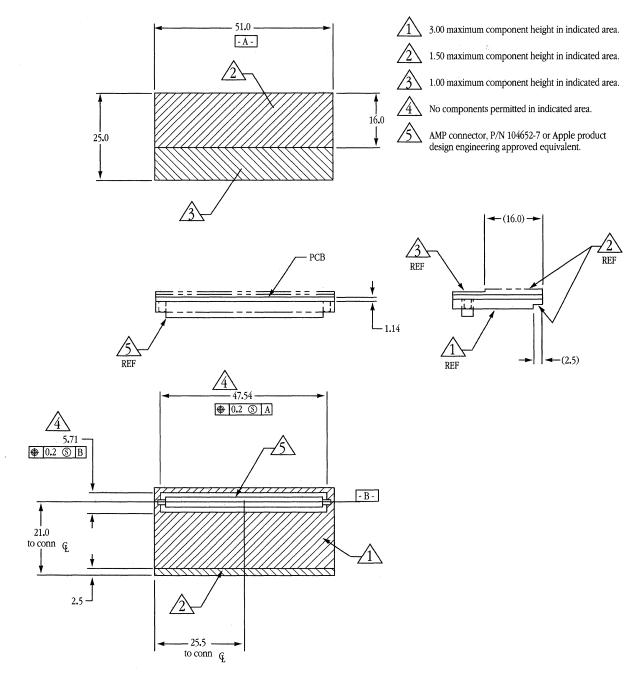

| Figure 20-8  | Location and pin orientation of modem and RAM<br>expansion connectors on the PowerBook 140 and<br>PowerBook 170 computers / 460 |

| Figure 20-9  | RAM expansion connector pinout for the PowerBook 140<br>and PowerBook 170 computers / 461                                       |

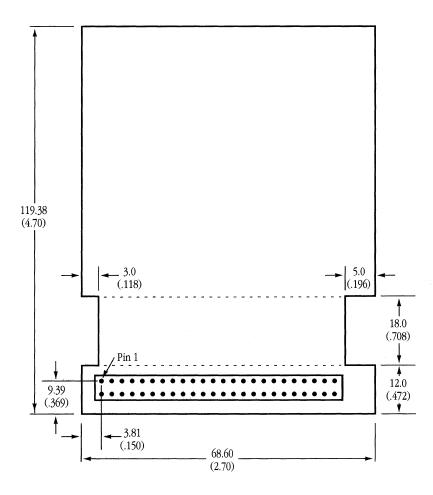

| Figure 20-10 | RAM expansion card design guide for the PowerBook 140 and PowerBook 170 computers / 466                                         |

| Figure 20-11 | PowerBook 100 memory map / 468                                                                                                  |

| Figure 20-12 | Location and pin orientation of modem and RAM<br>expansion connectors on the PowerBook 100<br>computer / 469                    |

| Figure 20-13 | RAM expansion connector pinout for the PowerBook 100 computer / 470                                                             |

| Macintosh Portable RAM expansion connector              |

|---------------------------------------------------------|

| signals / 449                                           |

| RAM expansion connector signal differences for the      |

| backlit Macintosh Portable / 450                        |

| Macintosh Classic RAM expansion connector signals / 456 |

| RAM expansion connector signals for the PowerBook 140   |

| and PowerBook 170 computers / 462                       |

| PowerBook 100 RAM expansion connector signals / 471     |

|                                                         |

## 21 ROM Expansion Interface / 475

| Figure 21-1 | Macintosh Portable ROM expansion connector                           |

|-------------|----------------------------------------------------------------------|

|             | pinout / 477                                                         |

| Figure 21-2 | Macintosh Portable ROM expansion card design guide / 479             |

|             | 0                                                                    |

| Figure 21-3 | Macintosh Classic II FPU /ROM expansion connector pinout / 487       |

| Figure 21-4 | Design guide for a Macintosh Classic II FPU/ROM expansion card / 491 |

|             |                                                                      |

| Table 21-1 | Macintosh Portable ROM expansion connector  |

|------------|---------------------------------------------|

|            | signals / 478                               |

| Table 21.2 | Magintoch Classic II FDU/POM expansion slot |

- Table 21-2Macintosh Classic II FPU/ROM expansion slot<br/>signals / 488

- Table 21-3

Macintosh Classic II ROM address allocations / 490

- Table 21-4Macintosh Classic II memory map summary / 490

## 22 Modem Expansion Interface / 493

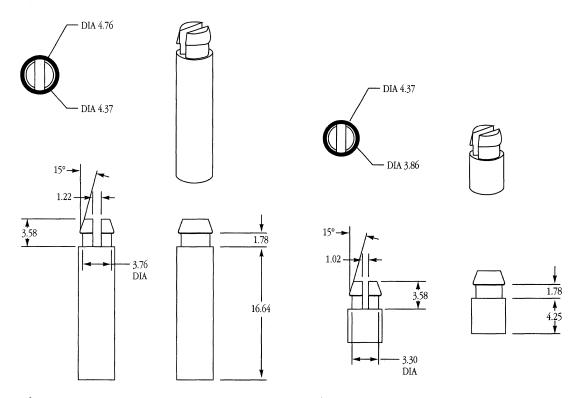

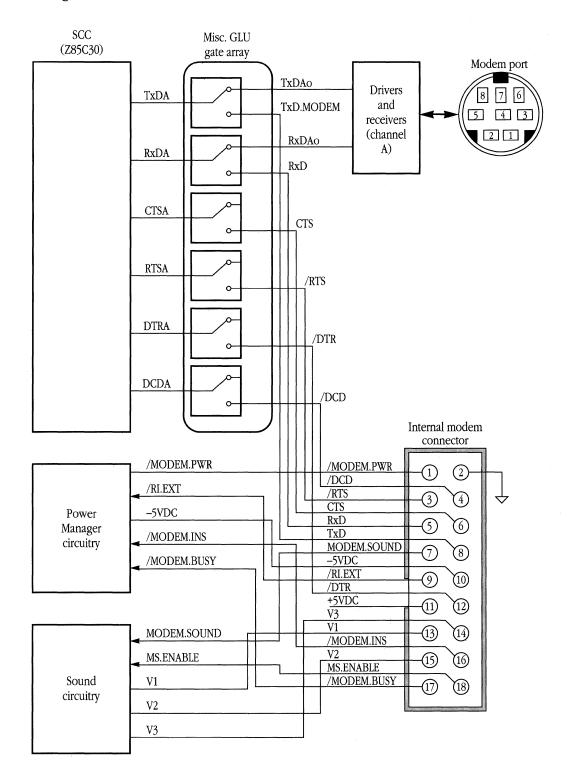

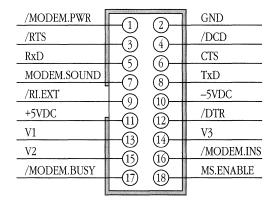

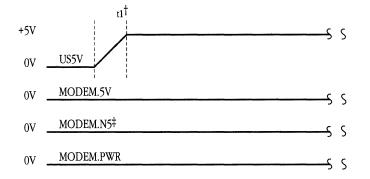

| Figure 22-1<br>Figure 22-2 | Modem interface for the Macintosh Portable / 495<br>Pinout of modem connector on the Macintosh<br>Portable / 496  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------|

| Figure 22-3                | Modem card design guide for the Macintosh<br>Portable / 498                                                       |

| Figure 22-4                | Cold-start timing diagram for the Macintosh<br>Portable / 500                                                     |

| Figure 22-5                | Warm-start timing diagram for the Macintosh<br>Portable / 500                                                     |

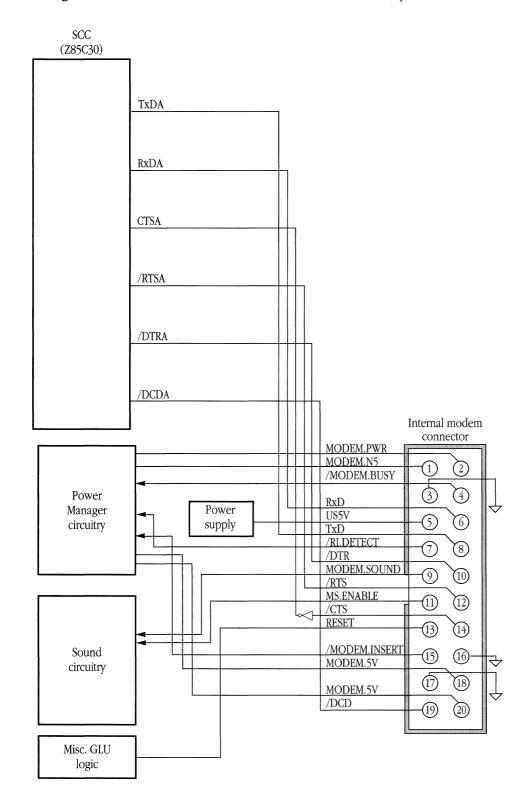

| Figure 22-6                | Modem interface for the PowerBook 140 and<br>PowerBook 170 computers / 503                                        |

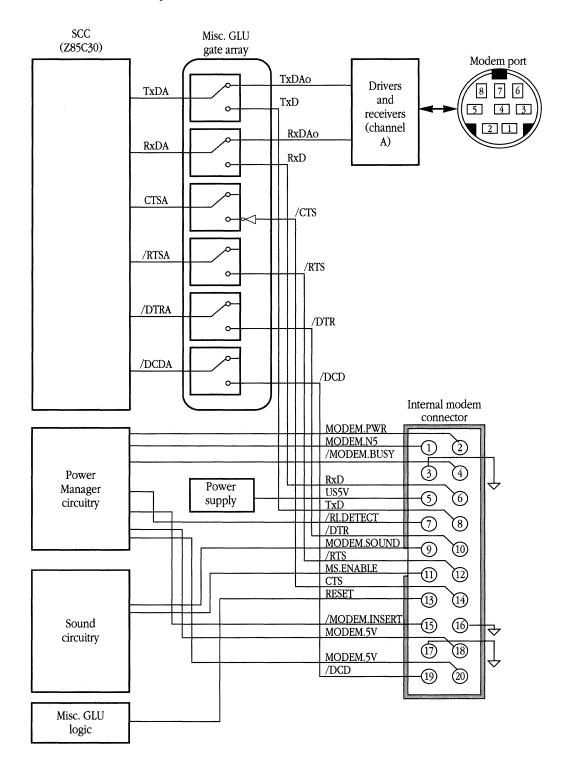

| Figure 22-7<br>Figure 22-8 | Modem interface for the PowerBook 100 computer / 504<br>Modem card design guide for the PowerBook<br>family / 508 |

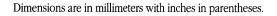

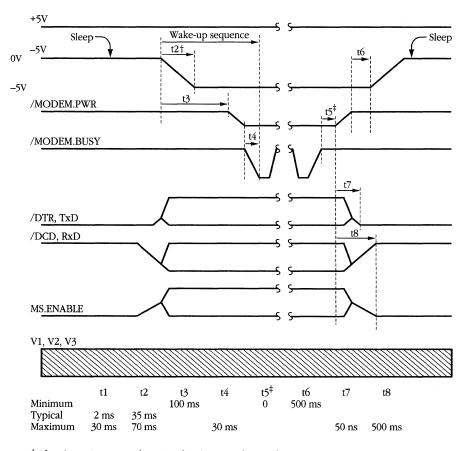

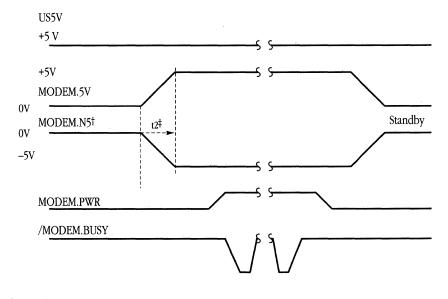

| Figure 22-9  | Modem cold-start timing diagram for the PowerBook                                       |

|--------------|-----------------------------------------------------------------------------------------|

|              | family / 511                                                                            |

| Figure 22-10 | Modem warm-start timing diagram for the PowerBook                                       |

|              | family / 511                                                                            |

| Figure 22-11 | Complete power-up/power-down sequence and timing diagram for the PowerBook family / 512 |

|              |                                                                                         |

Table 22-1Modem connector signal descriptions / 496

Table 22-2Modem connector signals for the PowerBook<br/>family / 505

#### 23 Macintosh IIci Cache Memory Expansion / 517

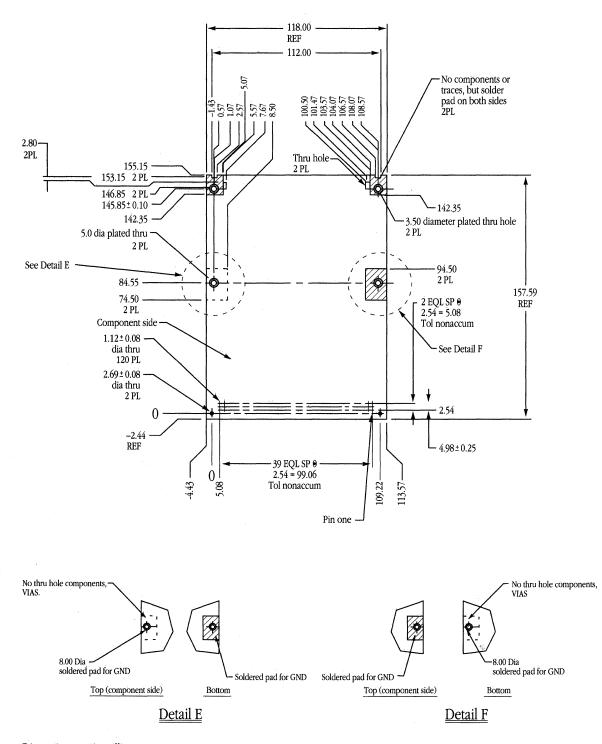

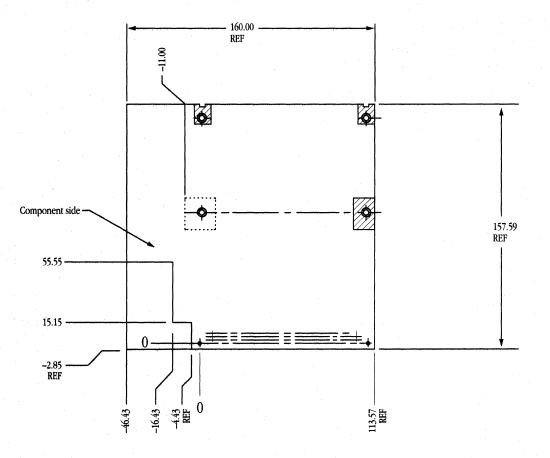

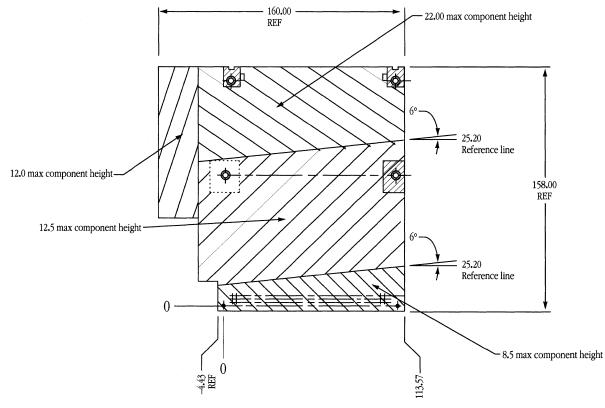

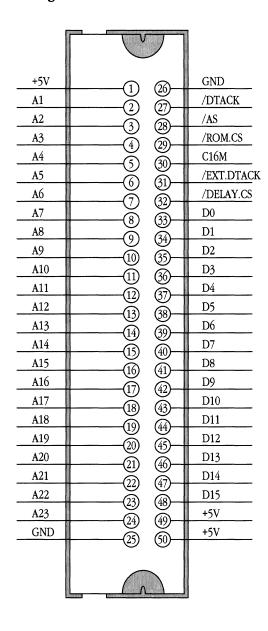

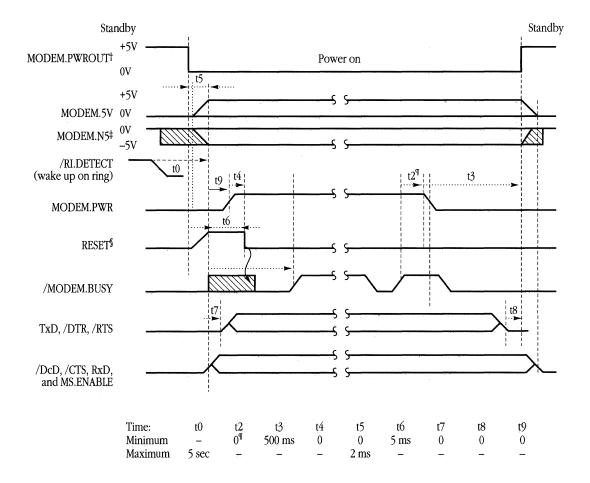

| Figure 23-1 | Macintosh IIci cache connector pinout | / 522 |

|-------------|---------------------------------------|-------|

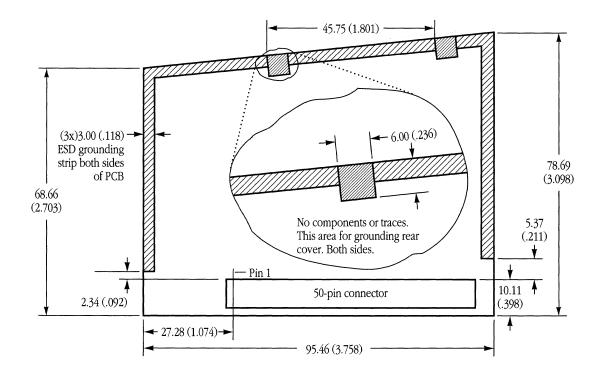

| Figure 23-2 | Cache card design guide / 529         |       |

| Tab | le 23-1 | Cache | memory | address | space , | / 520 |

|-----|---------|-------|--------|---------|---------|-------|

|     |         |       |        |         |         |       |

- Table 23-2Cache control trap / 520

- Table 23-3Macintosh IIci cache connector signal descriptions/ 523

- Table 23-4Macintosh IIci cache connector signals, loading or driving<br/>limits / 525

- Table 23-5Comparison of current limits for a Macintosh IIci cache<br/>card and a NuBus card / 530

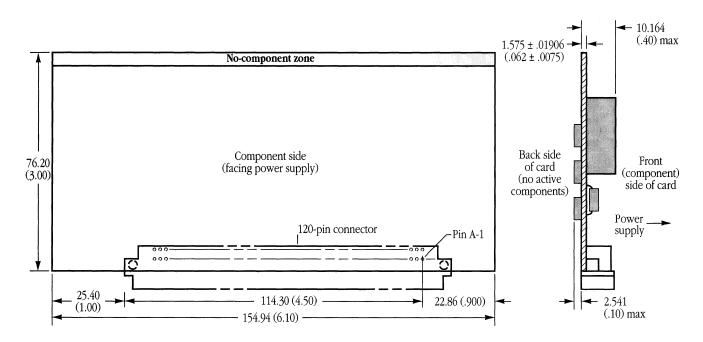

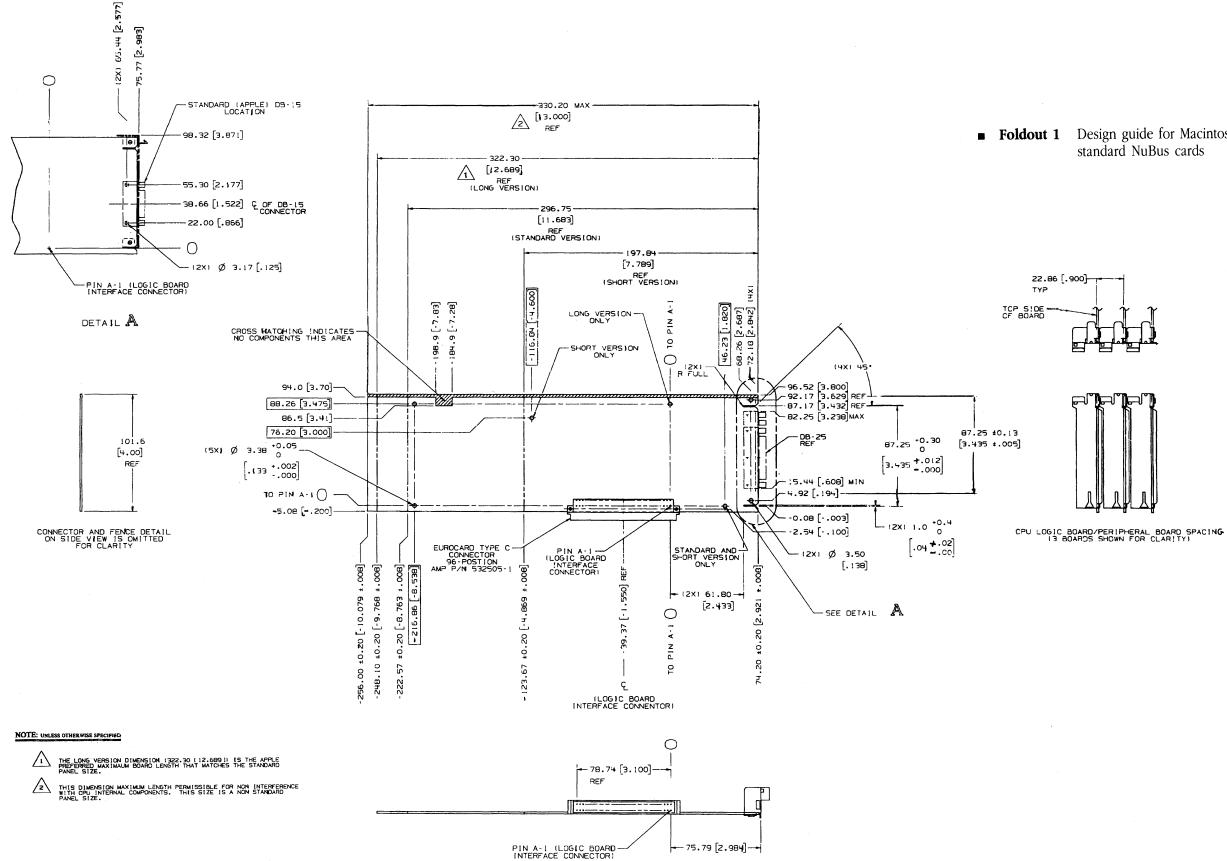

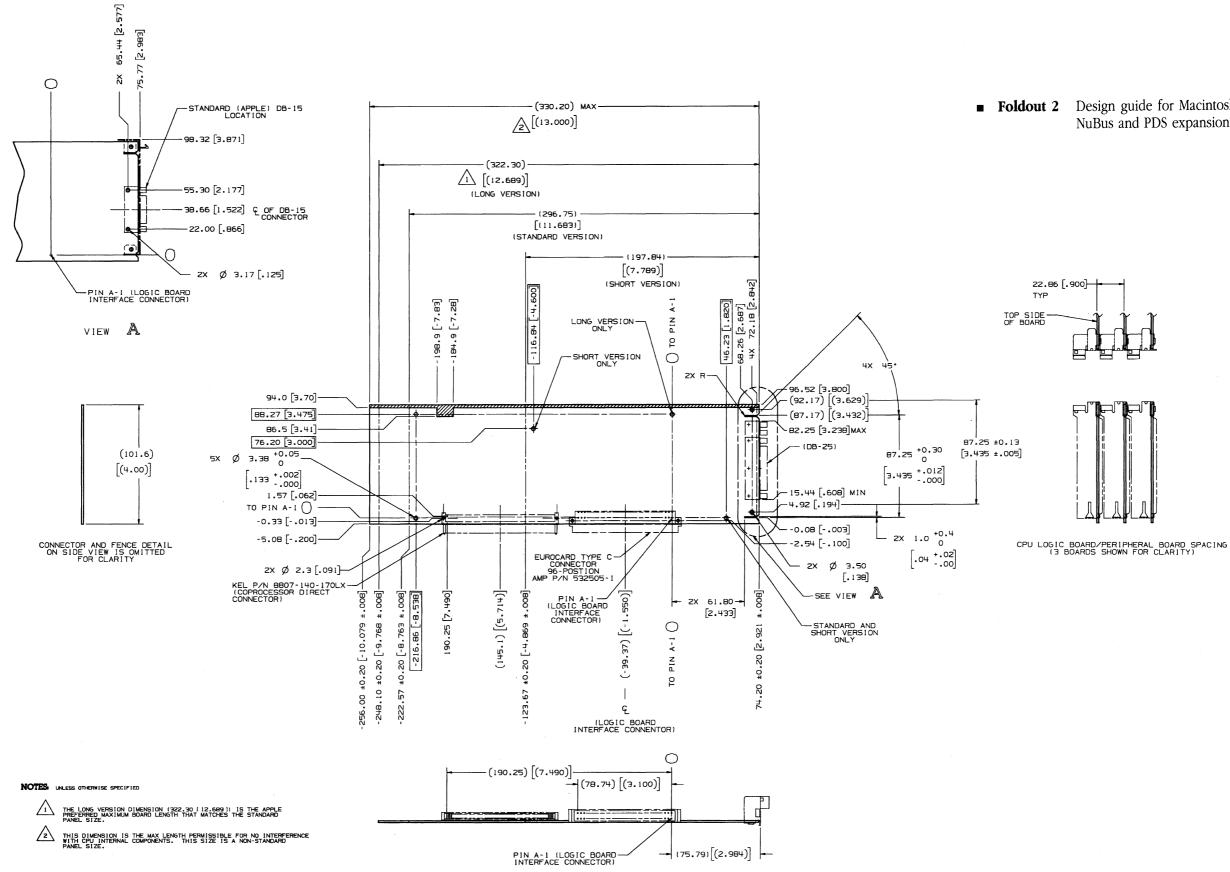

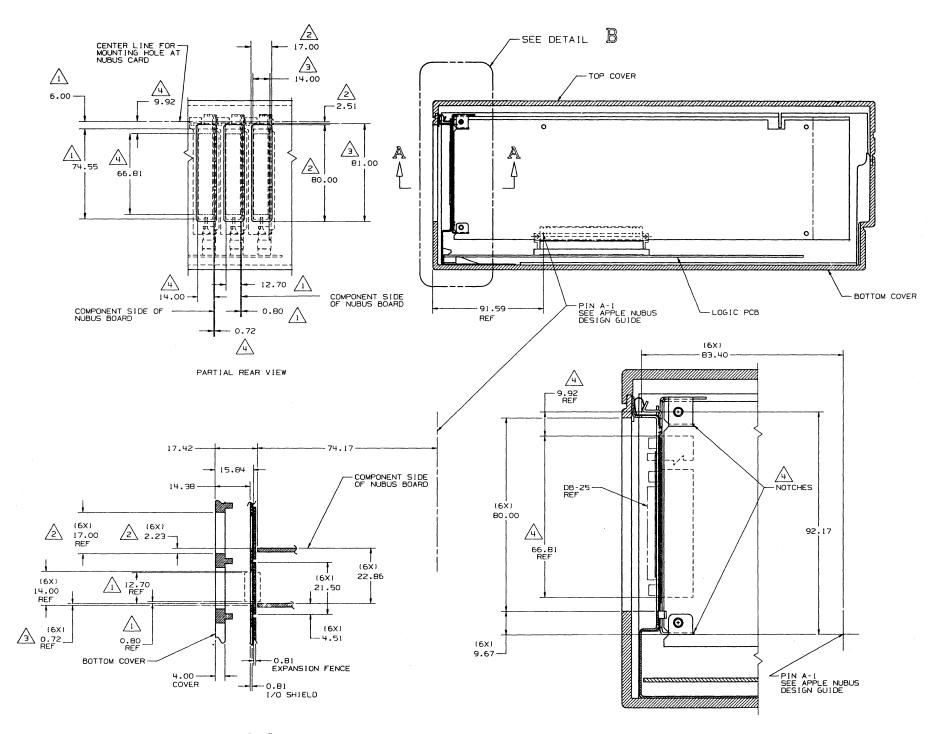

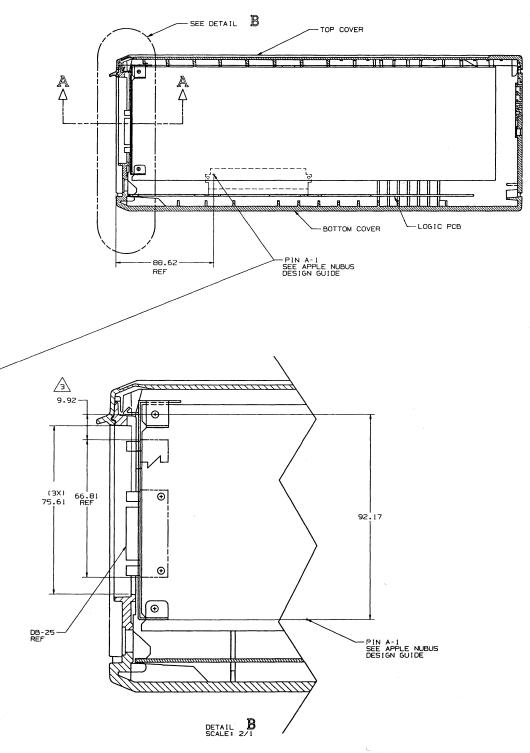

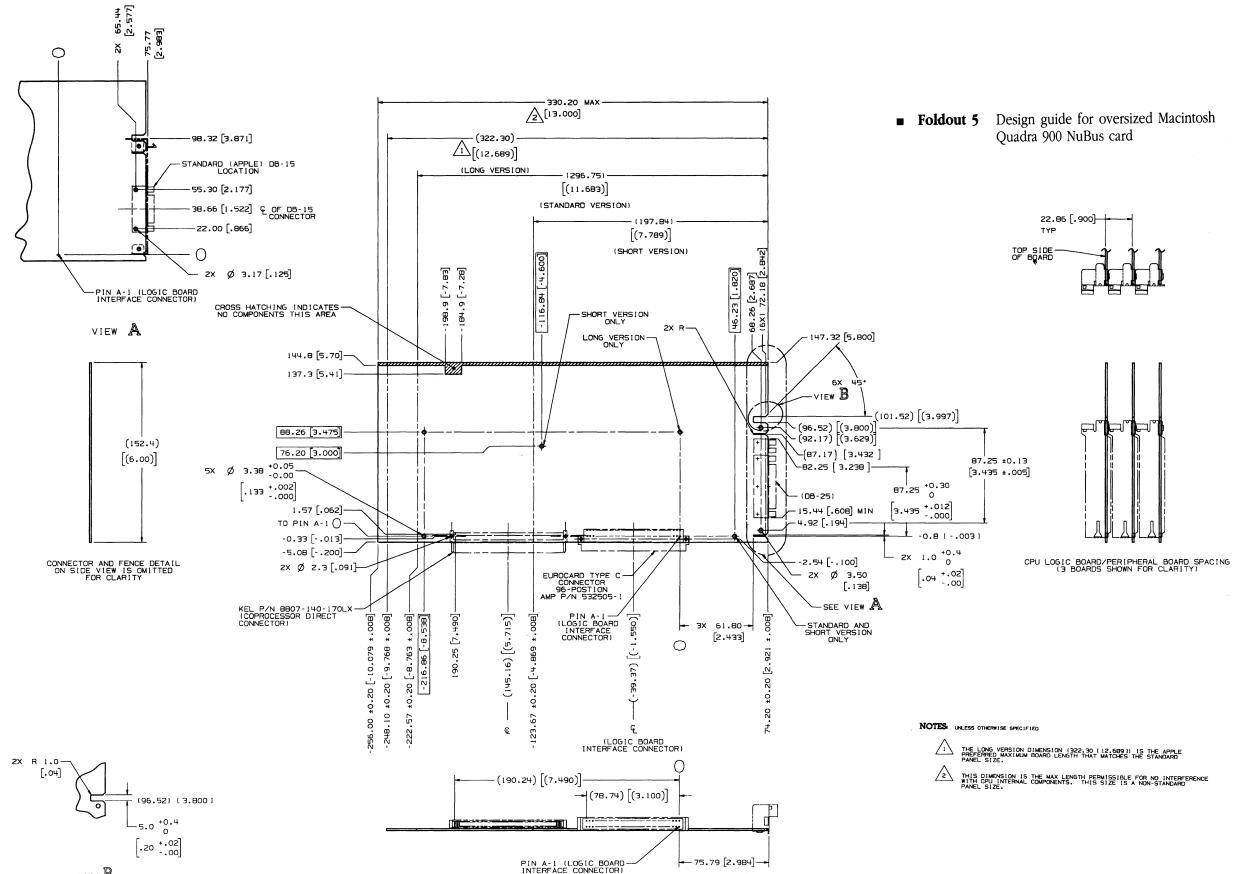

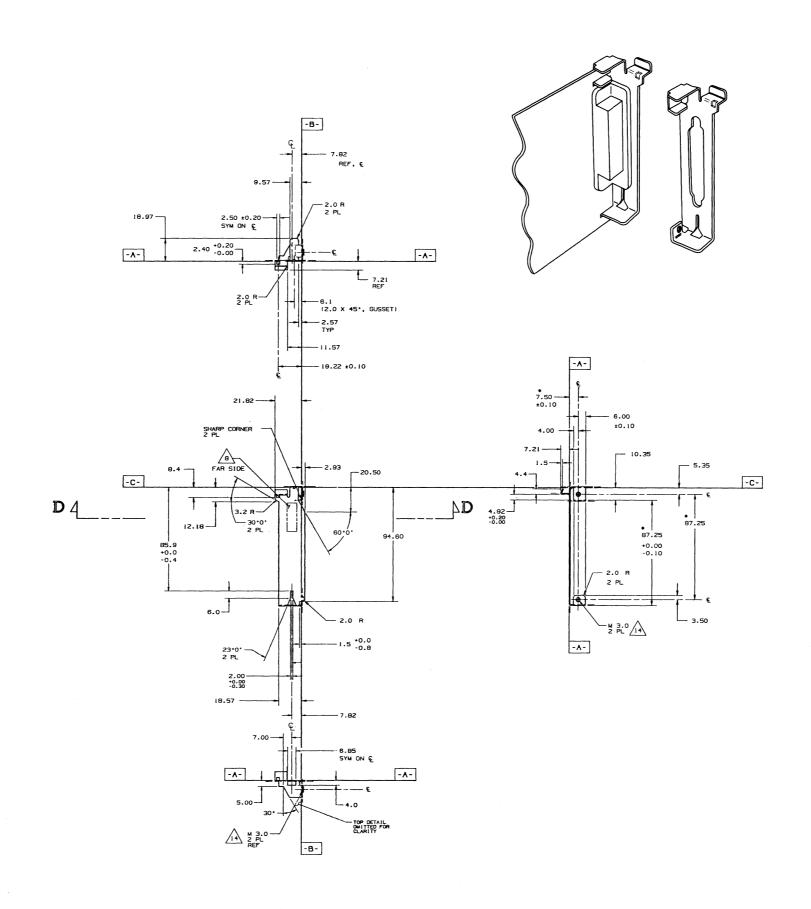

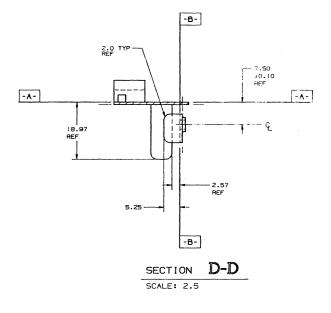

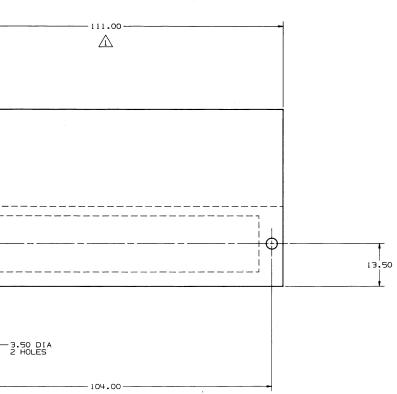

#### Foldouts / 621

| Foldout 1 | Design guide for Macintosh family standard NuBus cards / 623                                        |

|-----------|-----------------------------------------------------------------------------------------------------|

| Foldout 2 | Design guide for Macintosh Quadra–family NuBus and PDS expansion cards / 625                        |

| Foldout 2 | 1                                                                                                   |

| Foldout 3 | NuBus card clearance requirements for Macintosh II,<br>Macintosh IIx, Macintosh IIfx, and Macintosh |

|           | Quadra 900 computers / 627                                                                          |

| Foldout 4 | NuBus card clearance requirements for Macintosh IIcx,                                               |

|           | Macintosh IIci, and Macintosh Quadra 700                                                            |

|           | computers / 629                                                                                     |

| Foldout 5 | Design guide for oversized Macintosh Quadra 900 NuBus card / 631                                    |

| Foldout 6 | Connector shield for Macintosh II-family computer / 633                                             |

| Foldout 7 | NuBus Test Card (NTC) schematic diagram / 635                                                       |

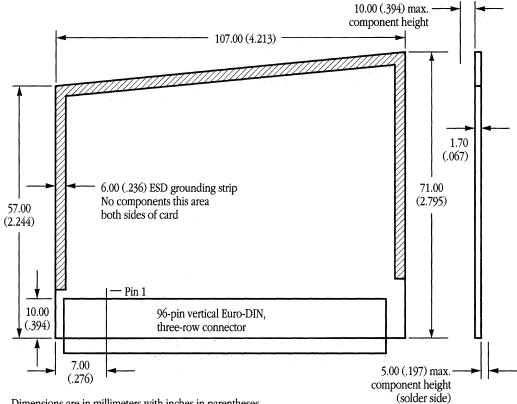

| Foldout 8 | Connector card design guide for Macintosh PDS computers / 637                                       |

| Foldout 9 | Design guide for Macintosh IIfx PDS expansion<br>card / 639                                         |

## Preface About This Book

The purpose of this book is to provide you, the developer, with the information that you need to develop expansion cards and device drivers for the Apple Macintosh family of computers. The introduction to this book discusses the Macintosh-family expansion strategy. It will give you an insight into Apple's plans for current and future hardware expansion for the Macintosh computer family. Following the introduction, the book is divided into three parts.

Part I defines the specifications of the NuBus<sup>™</sup> expansion interface, provides electrical and mechanical guidelines for designing NuBus expansion cards, and supplies information that is vital to the design of driver software.

Part II is devoted to the processor-direct slot (PDS) expansion interface. This part defines the design criteria and provides electrical and mechanical guidelines for designing expansion cards for Macintosh computers with processor-direct slots.

Part III gives design specifications and provides electrical and mechanical guidelines for expansion interfaces that have only one specific purpose.

## Design philosophy

In keeping with the Macintosh design philosophy, it is incumbent upon you, the card designer and driver writer, to make the installation of the card and its use by applications as transparent as possible. To the greatest extent possible, an application should rely on only a few high-level calls (if any) and not have to use low-level calls. To do otherwise jeopardizes the broadest potential use of your product.

## Conventions used in this book

The following visual cues are used throughout this manual to identify different types of information:

- *Note:* A note like this contains information that is interesting but is not essential for an understanding of the main text.

- $\triangle$  **Important** A note like this contains information that is essential for an understanding of the main text.  $\triangle$

▲ **Warning** A warning like this indicates a potential problem. ▲

When new or specialized terms are defined, they appear in **boldface.** Those terms are also defined in the glossary at the back of the book. The glossary contains additional terms of interest that are not boldfaced in the text.

Hexadecimal numbers are preceded by a dollar sign (\$). For example, the hexadecimal equivalent of decimal number 16 is written as \$10.

#### **xxxii** Designing Cards and Drivers for the Macintosh Family

In Part I, a NuBus word consists of 32 bits and a NuBus halfword consists of 16 bits. In Part II, a word consists of 16 bits and a longword consists of 32 bits. The two parts follow a different convention for their terminology to be consistent with the outside documentation to which each part is related: the Texas Instruments specification of the NuBus for Part I and the Motorola documentation for the MC68000, MC68020, MC68030, and MC68040 microprocessors for Part II.

Address ranges are given as "*lower address* through *higher address*" or "*lower address higher address*"; in either form the range is inclusive of the given endpoints. For example, an access range in memory is given in text as "\$00 0000 through \$3F FFFF," and in a table as "\$00 0000–\$3F FFFF."

A preceding slash is used to designate an active-low signal, for example, /ACK. A range of signals is designated like this, with the highest-numbered signal first: /AD31–/AD0. If there is more than one subrange in a set, the subranges are enclosed in angle brackets like this: </AD31–/AD29, /AD7–/AD0>.

Macintosh resource types are designated by enclosing them in single straight quotation marks, for example, 'INIT'.

The term *processor* is often used instead of *microprocessor* or *CPU. Processor* usually refers to the primary microprocessor on the main logic board, and *coprocessor* refers to an auxiliary processor such as the MC68882 floating-point unit on the main logic board or another processor on an expansion card.

The terms *processor-direct slot*, *PDS*, 68000 *Direct Slot*, 68020 *Direct Slot*, 68030 *Direct Slot*, and 68040 *Direct Slot* are all used to identify the processor-direct expansion interface associated with some Macintosh computers. Other documents may use a term such as *processor dependent slot* to identify this interface.

The following abbreviations are used:

| Κ    | 1024             |

|------|------------------|

| GB   | gigabyte         |

| Kbit | kilobit          |

| KB   | kilobyte         |

| kΩ   | kilohm           |

| Mbit | megabit          |

| MB   | megabyte         |

| μA   | microampere      |

| μs   | microsecond      |

| mA   | milliampere      |

| ms   | millisecond      |

| ns   | nanosecond       |

| Ω    | ohm              |

| pF   | picofarad        |

| RMS  | root mean square |

The distinction between boards and cards is as follows: boards are a permanent part of the computer (for example, the main logic board), whereas cards are insertable and can be added or exchanged for functional expansion or reconfiguration of the system.

#### The Courier font

Throughout the book, the names of specific software structures or fields within a structure are in the Courier font.

For example, suppose you see this sentence:

In the example of the SEXECBLOCK data type, the RevisionLevel field is always 02, the reserved field is always 00, and the CPUID field identifies the processor—01 for the 68000, 02 for the 68020, 03 for the 68030, and 04 for the 68040.

The word SExecBlock is in the Courier font to indicate that it is the name of a structure. The words RevisionLevel, reserved, and CPUID are in the Courier font to indicate that they are fields within the SExecBlock structure.

## About the mechanical drawings and design guides

Mechanical drawings of cards and connectors are provided in several chapters and in foldouts in the back of the book. Some of these drawings are design guides used within Apple Computer and were correct at the time of publication; they are, however, subject to change in the future.

## About the Macintosh technical documentation

Apple Computer, Inc., provides a suite of technical books that explain the hardware and software of the Macintosh family of computers.

The original Macintosh documentation consisted of the first three volumes of *Inside Macintosh*. Shortly after the introduction of the Macintosh Plus (with the 128 KB ROM), Volume IV of *Inside Macintosh* was released as a delta guide. That is, Volume IV covered only those aspects of the Macintosh Plus that were different from those in earlier Macintosh computers. Later, a fifth volume was added, called *Inside Macintosh*, Volume V. It is also a delta guide, covering the new and different features of the Macintosh SE and the Macintosh II computers. The latest volume, *Inside Macintosh*, Volume VI, describes the System 7 environment.

As the variety and the sophistication of Macintosh computers evolve, so does the documentation. To provide information that is comprehensive—and that provides answers to specific questions—Apple provides a whole family of books. Each of these books gives complete information about a single subject and may include some information that also appears in *Inside Macintosh. Guide to the Macintosh Family Hardware*, second edition, and this book are two of the books in this family.

For programmers and developers who are new to the Macintosh world, Apple has created two introductory books: *Technical Introduction to the Macintosh Family* and *Programmer's Introduction to the Macintosh Family*.

In addition to the books about the Macintosh itself, there are books on related subjects. Examples are a book about the user interface, a book about Apple's floating-point numerics, and the reference books for the Macintosh Programmer's Workshop.

Table P-1 gives a brief description of many of the books in the Macintosh technical documentation.

| Technical documentation                                 | Reference material                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Inside Macintosh                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Inside Macintosh, Volumes I–III                         | Complete reference to the Macintosh<br>Toolbox and Operating System for the<br>original 64 KB ROM                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Inside Macintosh, Volume IV                             | Delta guide to the Macintosh Plus (128 KB ROM)                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Inside Macintosh, Volume V                              | Delta guide to the Macintosh SE and Macintosh II (256 KB ROM)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Inside Macintosh, Volume VI                             | Description of System 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Inside Macintosh X-Ref, revised edition                 | A single general index to eleven technical<br>reference books for the Apple Macintosh fam<br>of computers: <i>Inside Macintosh</i> , Volumes I–VI<br><i>Inside the Macintosh Communications Toolbo</i> .<br><i>Programmers Introduction to the Macintosh</i><br><i>Family; Technical Introduction to the Macinto</i><br><i>Family; Designing Cards and Drivers for the</i><br><i>Macintosh Family, second edition; and Guide</i><br><i>the Macintosh Family Hardware, second edition</i> |  |

| Introductory books                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Technical Introduction to the<br>Macintosh Family       | Introduction to the Macintosh software and<br>hardware; explains concepts and terminology<br>that are specific to the Macintosh family<br>of computers.                                                                                                                                                                                                                                                                                                                                  |  |

| Programmer's Introduction to the<br>Macintosh Family    | Introduction to programming the Macintosh system for programmers who are new to it                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Single-subject books                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Designing Cards and Drivers for the<br>Macintosh Family | Hardware and device-driver reference for the expansion capabilities of the Macintosh computer family                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Guide to the Macintosh Family Hardware                  | Hardware reference and developer's guide for the Macintosh computer family                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                         | (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

### **Table P-1** Macintosh technical documentation

| Technical documentation                                                                                                                     | Reference material                                                                                                                                                                                                                                                                          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Related books                                                                                                                               |                                                                                                                                                                                                                                                                                             |  |

| Human Interface Guidelines:                                                                                                                 | Detailed guidelines for developers                                                                                                                                                                                                                                                          |  |

| The Apple Desktop Interface                                                                                                                 | implementing the Macintosh user interface                                                                                                                                                                                                                                                   |  |

| Apple Numerics Manual                                                                                                                       | Description of the Standard Apple Numerics<br>Environment (SANE), an IEEE-standard<br>floating-point environment supported by all<br>Apple computers                                                                                                                                        |  |

| Macintosh Programmer's Workshop<br>3.0 Reference                                                                                            | Workshop (MPW), Apple's software computers development environment for all Macintosh                                                                                                                                                                                                        |  |

| Apple Developer Notes                                                                                                                       |                                                                                                                                                                                                                                                                                             |  |

| Macintosh IIsi, LC, and Classic<br>DeveloperNotes, APDA publication<br>number M0991LL/A                                                     | Interim hardware reference and<br>developer's guide for the Macintosh<br>IIsi, Macintosh LC, and Macintosh<br>Classic computers; obsolete when the<br>information has been incorporated<br>into the third edition of <i>Guide to the</i><br><i>Macintosh Family Hardware</i>                |  |

| Macintosh Classic II,<br>MacintoshPowerBook Family, and<br>Macintosh Quadra Family Developer<br>Notes, APDA publication number<br>R0143LL/A | Interim hardware reference and<br>developer's guide for the Macintosh<br>Classic II, Macintosh PowerBook,<br>and Macintosh Quadra computers;<br>obsolete when the information has<br>been incorporated into the third<br>edition of <i>Guide to the Macintosh</i><br><i>Family Hardware</i> |  |

### **Table P-1** Macintosh technical documentation (continued)

# How to get more information

Several organizations exist that provide support for Macintosh hardware and software developers. This section tells you how to contact APDA, Apple user groups, and Apple Developer Services.

### APDA

APDA offers convenient worldwide access to over three hundred development tools, resources, and training products, and to information for anyone interested in developing applications on Apple platforms. Customers receive the quarterly *APDA Tools Catalog*, featuring the most current version of Apple development tools and the most popular third-party development tools. Ordering is easy; there are no membership fees, and application forms are not required for most of our products. APDA offers convenient payment and shipping options, including site licensing.

To order products or get additional information, contact

APDA Apple Computer, Inc. 20525 Mariani Avenue, M/S 33-G Cupertino, CA 95014-6299

800-282-2732 (United States) 800-637-0029 (Canada) 408-562-3910 (International) Fax: 1-408-562-3971 Telex: 171-576 AppleLink address: APDA

### User groups

Apple user groups are associations of individuals who share information about Apple computers and related products. For information about Apple user groups in your area, call this toll-free number:

800-538-9696

Ask for extension 500.

### **Apple Developer Services**

Apple's goal is to provide developers with the resources they need to create new Applecompatible products. Apple offers two programs: the Partners Program, for developers who intend to resell Apple-compatible products; and the Associates Program, for developers who do not intend to resell Apple-compatible products and for other people involved in the development of Apple-compatible products.

As an Apple Partner or Associate, you will receive monthly mailings including a newsletter, Apple II and Macintosh Technical Notes, pertinent Developer Program information, and all the latest news relating to Apple products. You will also receive the *Macintosh Services Directory* and automatic membership in APDA. You'll have access to developer AppleLink and to Apple's Developer Hotline for general developer information.

As an Apple Partner, you'll be eligible for discounts on equipment and you'll receive technical assistance from the staff of Apple's Developer Technical Support department.

For more information about Apple's developer support programs, contact Apple Developer Programs at the following address:

Apple Developer Programs Apple Computer, Inc. 20525 Mariani Avenue, M/S 51-W Cupertino, CA 95014-6299

# Introduction Expansion Strategy for the Macintosh Family

Apple has decided on an expansion strategy that limits the Apple Macintosh family of computers to three distinctly different internal architectural expansion configurations: the NuBus™ expansion interface, the processor-direct slot (PDS) expansion interface, and the application-specific expansion interface. Limiting the expansion architecture to three categories ensures that expansion card developers, both internal and external to Apple, have some degree of predictability and stability in their expansion card designs. Since Apple depends upon you, the third-party hardware developer, to create the expansion cards that enhance many Macintosh computers, it is important that you are aware of this expansion strategy. This section gives you the information you will need to make good decisions on what cards to develop, and for what Macintosh models, both present and future.

# Limiting the number of expansion interfaces

Apple's implementation of NuBus represents a mature expansion mechanism that has been adopted as the primary expansion vehicle for the Macintosh family of modular computers and can be supported across a variety of Macintosh products.