# Micron Technology Memory Applications Group

8-Bit Color Video Board for the Macintosh SE/30 1024x768 Xceed SE/3010-78

> C. Snodgrass L. Mills Version 1.00 August 15, 1989

## For Internal Use Only

Glen Atkins Greg Blodgett MARK DAY Laura Mills Chuck Snodgrass Tom Stamm

8/15/89

SE/3010-78

1

# CONTENTS

| Chapter 1  | Introduction             | 3  |

|------------|--------------------------|----|

| Chapter 2  | Macintosh SE/30          | 4  |

| Chapter 3  | Theory of Operation      | 10 |

| Chapter 4  | PAL Description          | 20 |

| Chapter 5  | Parts List               | 35 |

| Chapter 6  | Video Board Testing      | 37 |

| Chapter 7  | Test Points/Oscilloscope | 38 |

| Appendix A | Test Software            | 39 |

| Appendix B | Schematics               | 44 |

## Chapter 1 Introduction

The Micron Xceed SE/3010-78 is an 8-bit board for the Macintosh SE/30. The standard Macintosh SE/30 video is a built-in black-and-white screen, 512x342 pixels. For Micron's 8-bit color video board, the pixel data is represented by 1, 2, 4, or 8 data bits at 1024x768 resolution. This allows a selection of over 16 million colors (16,777,216) for each pixel, but only 256 colors may be shown on the monitor at one time. The 24 bits of information required for the monitor are obtained from a look-up table, using the 8 bits of board data as the table index.

The eight bits representing a color are converted to an RGB value (RGB monitor = red, green, blue) using the look-up table. The pixel color is a combination of the red, green, and blue component values obtained from the table. Each component color requires eight bits of information, converted to an analog voltage level with a D/A converter. These three resulting voltages, one for each component color, go to the monitor to create the color for a single pixel. The pixels appear left-to-right, top-to-bottom on the monitor; scanning across each line then down to the next line. The screen is 1024x768 pixels, requiring 3/4 MB of on-board memory (768KB) to store a single screen of data.

Besides the Video RAMs (VRAMs) to store the picture data, there is a ROM on the board that contains the video board driver and information that enables the Macintosh to identify the board. When the computer is powered up, it checks for any boards by reading the information in the ROM. Ten PALs control most board functions. The video board is in slot A.

## Chapter 2 Macintosh SE/30

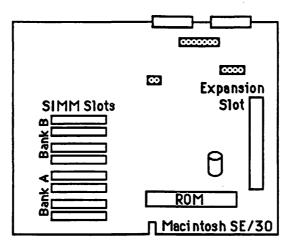

The Macintosh SE/30 contains the Motorola 68030 microprocessor and one expansion slot, which may be numbered 9, A, or B hex. The SE/30 is essentially a Macintosh IIx computer in a smaller box. The expansion slot, though, comes off of the processor bus. The SE/30 does not have any NuBus expansion slots.

While the Macintosh SE/30 has 32 address lines, only 24 of these are used in the normal (default) mode. The computer can be placed in 24-bit or 32-bit mode similar to the Macintosh II. The 8-bit video board's ROM and VRAM array addresses, however, are all directly accessible in normal mode.

| Address                | Description                                             |

|------------------------|---------------------------------------------------------|

| 00000000 - 000FFFFF    | RAM (minimum configuration)                             |

| 00100000 - 00CFFFFF    | RAM (expansion area)                                    |

| 00D00000 - 3FFFFFF     | RAM (undefined)                                         |

| 40000000 - 4007FFFF    | ROM Bank O (minimum configuration)                      |

| 40080000 - 4FFFFFF     | ROM (undefined)                                         |

| 5000000 - 5000 1FFF    | VIA1 (x0200)                                            |

| 50002000 - 50003FFF    | VIA2 (x0200)                                            |

| 50004000 - 50005FFF    | SCC (×0002)                                             |

| 50006000 - 50007FFF    | SCSI (Handshake)                                        |

| 500 10000 - 500 1 1FFF | SCSI (x0010)                                            |

| 500 12000 - 500 13FFF  | SCSI (Pseudo DMA)                                       |

| 50014000 - 50015FFF    | Sound                                                   |

| 50016000 - 50017FFF    | S₩IM                                                    |

| 50018000 - 57FFFFFF    | (undefined)                                             |

| 58000000 - 5FFFFFF     | 030 Direct Slot expansion (if pseudo-NuBus is not used) |

| 60000000 - F8FFFFFF    | expansion (undefined)                                   |

| F9000000 - FBFFFFFF    | expansion pseudo-NuBus slots                            |

| FC000000 - FDFFFFFF    | expansion (undefined)                                   |

| FE000000 - FE00FFFF    | video RAM space                                         |

| FEFF0000 - FEFFFFFF    | video ROM space                                         |

| FF000000 - FFFFFFF     | expansion (undefined)                                   |

Table 2-1 Address Mapping

The Macintosh SE/30 uses memory-mapped I/O. Each device in the system can be accessed by reading or writing to specific address locations in the address space of the computer. The addressing for a card in a slot is directly dependent on the slot number. The SE/30 has three slot numbers possible for a single slot. The slot number is defined in hardware on the expansion board and cannot be changed.

4

The slot in the Macintosh SE/30 can be directly accessed in the 32-bit mode at the address found by multiplying the slot ID by 10,000,000 hex (s000 0000sFFF FFFF hex); this is the Super Slot Space. The slot can also be found at the Slot Space Fs00 0000-FsFF FFFF hex (s = slot ID, 9-B) when in the 24-bit default operating mode. Each physical slot has both the slot and super slot space allocated to it. In 24-bit mode the AMU (Address Mapping Unit) or PMMU (Paged Memory Management Unit), whichever is present, will convert s0 0000 to Fs00 0000.

#### 2.1 Bus Signals

The Macintosh SE/30 Direct Slot expansion bus is based on the Motorola 68030 microprocessor. It is machine-specific, not a general-purpose bus like NuBus. The card design may be similar to NuBus (Pseudo-NuBus), with the same type of ROM and addressing, but the pinout and signals differ. The SE/30 Direct Slot uses a 120-pin 16MHz synchronous bus. Words, halfwords, and bytes can be read and written, but the bus is optimized for word transfers. All signals are active low.

| Bit 31     |          |        | Bit 0  |

|------------|----------|--------|--------|

| Dir        | ect Slot | Word   |        |

| Halfword 1 |          | Halfw  | ord O  |

| Byte 3     | Byte 2   | Byte 1 | Byte O |

Table 2-2 Bus Data

The bus specification divides the signals into five types:

<u>Power:</u> +5V, +12V, -12V, and -5V.

Data and Address Lines: A0-A31, D0-D31.

Control Lines: \STERM, SIZ0-SIZ1, FC0-FC2, \RESET, \BERR, R/W, \AS Clocks: CPUclock and C16M (for the SE/30, these are identical 16 MHz

signals).

Machine-Specific Signals: PWROFF, \BUSLOCK, \IRQ1-\IRQ3, \TM0A-\TM1A, \NuBus, CPUclock.

The connector contains three rows of pins (see Appendix B). The Micron video board does not use all of the signals on the expansion bus. A 'high' level is > 2V, 'low' level < 0.8V.

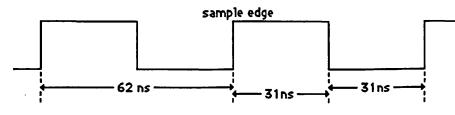

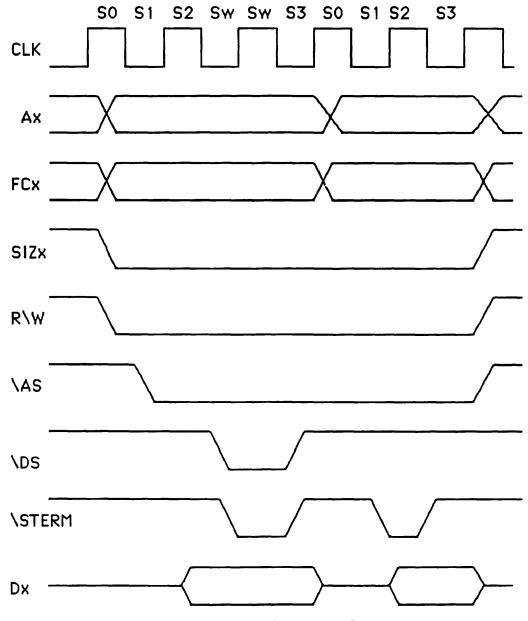

Figure 2-1 System Clock

## 2.2 READ-WRITE-READ CYCLE

The read-write-read transaction is shown below. It may take longer than shown, but the timer on the SE/30 main logic board will generate a bus error signal when the address strobe is asserted for longer than  $\approx$ 20 microseconds.

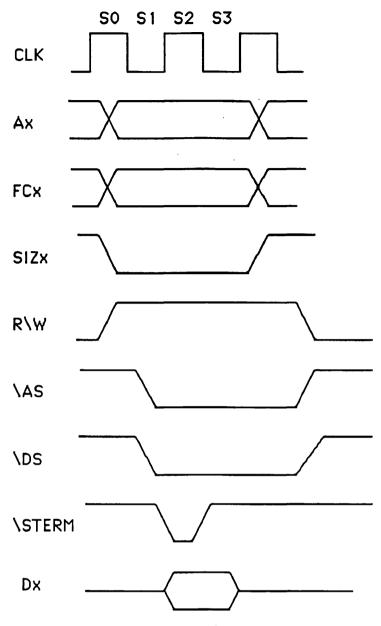

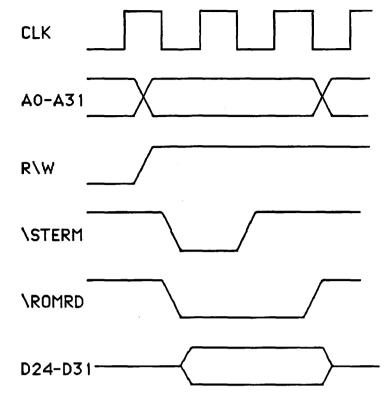

#### SE/30 Read/Write Cycles

(All accesses to the video card are 32 Bit Synchronous)

#### **Read Cycle**

At state zero (S0) the SE/30 drives Ax, FCx, SIZx, and R\W with an address, type of function, size of data transfer, and read command. Half a clock cycle later, during state one (S1), \AS and \DS are asserted by the SE/30 to tell the external device that the address lines are now valid and data may be placed on the bus. By the end of S1 the external device will assert \STERM. \STERM tells the SE/30 that the read data will be valid by the next falling clock. At the start of state two (s2) the external device places data on the bus and terminates \STERM. The SE/30 latches in the data at the end of S2. State three (S3) provides the data hold time as required.

#### Write Cycle

At state zero (S0) the SE/30 drives Ax, FCx, SIZx, and R\W with an address, type of function, size of data transfer, and write command. Half a clock cycle later, during state one (S1), \AS is asserted by the SE/30 to tell the external device that the address lines are valid. At the beginning of state two (S2) the SE/30 looks for \STERM. If \STERM is not present the SE/30 will insert a wait state. Also during S2 the SE/30 will drive the data bus with valid data. During a wait state (SW) the SE/30 asserts \DS to tell the external device that the bus still contains valid data. At the start of each wait state the SE/30 will check for \STERM. If \STERM is not present the SE/30 will check for \STERM. If \STERM is not present the SE/30 will check for \STERM. If \STERM is not present the SE/30 will insert another wait state, if

\STERM is present, the SE/30 will terminate the write cycle in the following state (S3). During state three (S3) the address and data lines remain valid.

Figure 2-3 Read-Write-Read Cycles

8/15/89

# 2.3 System Board

Figure 2-4 Macintosh SE/30 System Board

8/15/89

## Chapter 3 Theory of Operation

August 11, 1989 Chuck Snodgrass x3841

| Architecture         | <br>10 |

|----------------------|--------|

| 3.1 Bus Interface    | <br>10 |

| 3.2 Video Timing     | <br>15 |

| 3.3 RGB Video Output | <br>17 |

#### Architecture

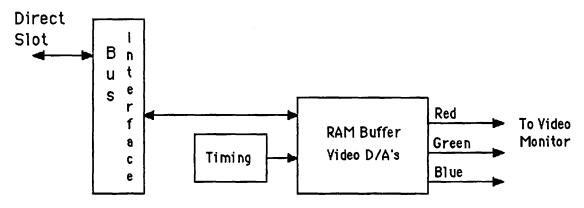

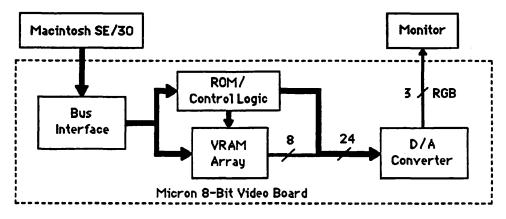

The video board can be broken down into three functional blocks: the bus interface, the video timing and the video output. The Macintosh SE/30 uses a Motorola 68030 processor which communicates with the video board over the bus. The video timing section of the board determines the video rate and format. The video output section drives out analog RGB video to a monitor.

Figure 3-1 Block Diagram

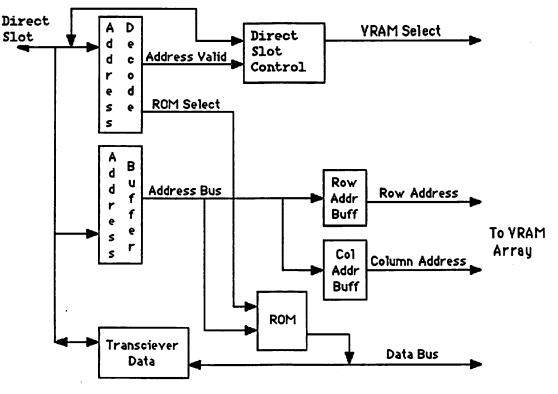

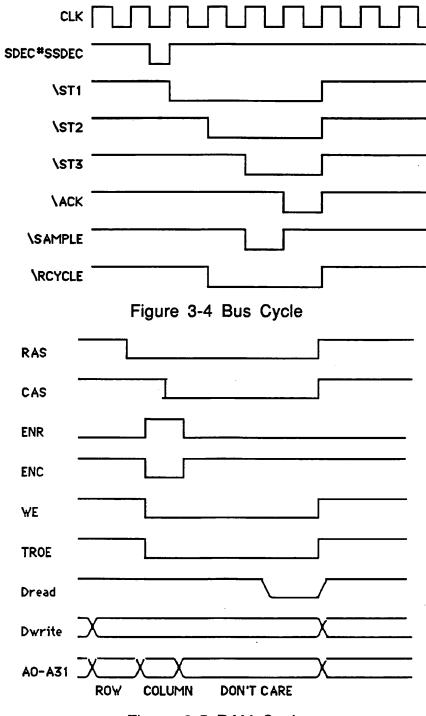

## 3.1 Bus Interface

The SE/30 bus is a 32 bit 16MHz bus. In addition to 32 bits of address and data, there are several control lines. For write cycles, the address is also driven on the first rising edge of the clock and then the data is driven on the second and remains until a transfer acknowledge signal is received (\STERM low) or until a timeout occurs. Bus timeouts will occur if no acknowledge is received within  $\approx$ 20 microseconds of a cycle start. Typically a bus timeout will result in a system error which will require the user to reboot the Macintosh. The \AS signal is used to indicate the beginning of a bus cycle if the \STERM signal is high. The \FC0 and \FC1 control lines are used at the beginning of a cycle to define the type of cycle to be performed, and at the end of the cycle

\STERM is used to determine when the cycle was completed. The board is accessed when the address (A24-A31) is either \$FA of \$AX and comes up in one of three modes. The mode is determined by A17, A18, and A19.

| MODE  | A19 | A18 | A17 |

|-------|-----|-----|-----|

| Video | 0   | X   | X   |

| RAM   | 1   | 0   | 0   |

|       | 1   | 0   | 1   |

| D/As  | 1   | 1   | 0   |

| ROM   | 1   | 1   | 1   |

Table 3-1 Board Access

On power up the Bus reset signal is driven low to initialize all boards on the Bus. Reset is used by the video card to terminate any Bus cycles and disable the 60Hz interrupt. After reset the 68030 reads from the highest address of each Bus slot. By definition the declaration ROM must reside at this address. The ROM is only required to occupy eight of the 32 data bits on the bus. This puts valid ROM data at every fourth byte of address space. The video board ROM uses byte lane zero (the first byte lane, bus bits D0-D7). To determine the byte lane(s) being used, the processor reads all four bytes and looks for a valid data value in one or more of the byte lanes. For each valid value it continues reading from the specified byte lane(s) looking for a predefined sequence of numbers. If the numbers are correct, the processor will use only the specified byte lane(s) for future ROM accesses (refer to Cards and Drivers for more information concerning bus signals and byte lanes). The processor reads the ROM which contains information describing the board, and then copies the driver from the ROM into system RAM on the SE/30 motherboard. The driver open routine is then executed. This routine initializes the video buffer by writing a gray pattern (black and white dots) to the VRAM array. Then it sets the VIDON signal TRUE which enables the 60Hz slot interrupt and the video output. The 60Hz interrupt signals the processor to update the cursor position. When the system detects a slot interrupt, control is transferred to the driver which clears the interrupt via a MODACC write, calls for a cursor position update and returns control to the system.

Information stored in the declaration ROM includes:

- byte lane #0 is used for reading the ROM

- verification code to demonstrate the existence of the ROM

- 1,2,4, or 8 bits per pixel

- 1024x768 bits resolution

- single display page

- first pixel is located at an offset of 0 from the slot base address

- there is an offset of 400(Hex) between scan lines

- · location of video driver in the ROM

- video driver

- checksum of the ROM

Figure 3-2 Bus Interface Block Diagram

Figure 3-3 Declaration ROM Access from Bus

The address range of the ROM is FAXFC000 - FAXFFFFF. The ROM is actually only 4096 bytes long occupying 16382 bytes of address space due to being resident on only the zeroth byte lane. The ROM will appear to occupy multiple positions in this range of addresses (addresses wrap around) since only the MSB address lines are decoded to determine ROM access requests.

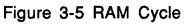

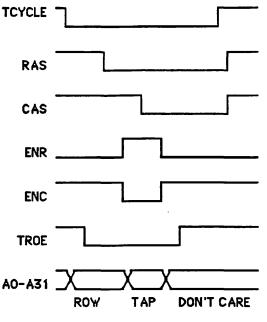

During normal operation the processor will write to and read from the video buffer. The accesses to the buffer are synchronized with the horizontal blanking intervals so that they do not interfere with the TRANSFER cycles which are required to update the SRAM portion of the VRAM and the video display.

The video RAMs are arranged in 3 banks, each one 32 bits wide. The video RAM consists of 2 parts, DRAM which can be updated at anytime (except during a transfer cycle) and SRAM which receives data via a TRANSFER cycle from the DRAM, which occurs for every horizontal trace. The TRANSFER cycle timing is independent of any bus timing and is generated around the horizontal synch signal. A TRANSFER cycle also generates a RAMHOLD which disables processor accesses to the RAM. Data enters the VRAMs through a 32 bit parallel path and leaves through one of four 8 bit serial paths. The serial pixel data is interleaved from the 4 shift registers. Data from these shift registers is formatted to the appropriate number of bits per pixel then output to the D/As.

Figure 3-6 Transfer Cycle

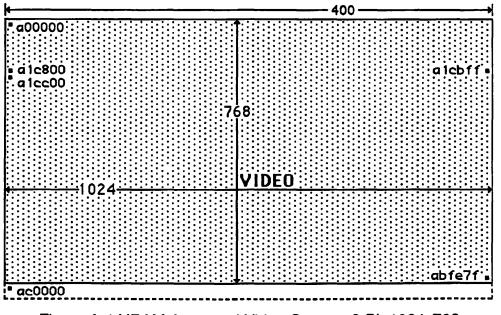

The RAM occupies an address range of A00000 - ABFFFF. All of the 1024x768 pixels are valid. This rectangle begins at A00000 (pixel #0 on line #1) and ends at ABFFFF (pixel #1023 on line #768).

Before shutting down the computer the operating system will execute a close routine also found in the video driver portion of the declaration ROM. This routine disables the slot interrupts which also disables the video output, and then returns control to the operating system.

To enable the slot interrupt and the video output, FFFFFFFF is written to any address in the range FAXE0000-FAXFFFFF. To disable the interrupt and the video output, 0 is written to any address in the range FAXE0000-FAXFFFFF. Enabling or disabling the interrupt will also clear the interrupt.

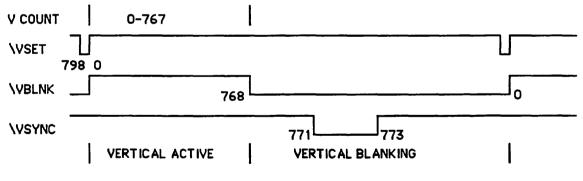

#### 3.2 Video Timing

The video timing portion of the board generates the horizontal and vertical timing signals for the display. The horizontal and vertical sections are similar in design, using counters and PALs. On power up the output count of the counters is unknown, but they will count up to a point where they will cause the PAL to reload the counters to a known value. The horizontal counter is used to address pixels on a line (RAM column address). Counts 108-620 represent visible pixels. On count 662 the \SYNC (sync) signal goes low triggering the horizontal retrace of the monitor. On count 665 a signal called \HSET goes low causing the horizontal counters to reload. The \HSET signal also clocks the vertical counters and PAL. The clock frequency and the counter preset values determine the line frequency of the video.

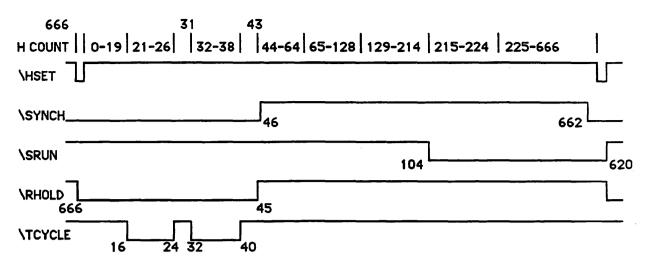

Figure 3-7 Horizontal Timing Signals

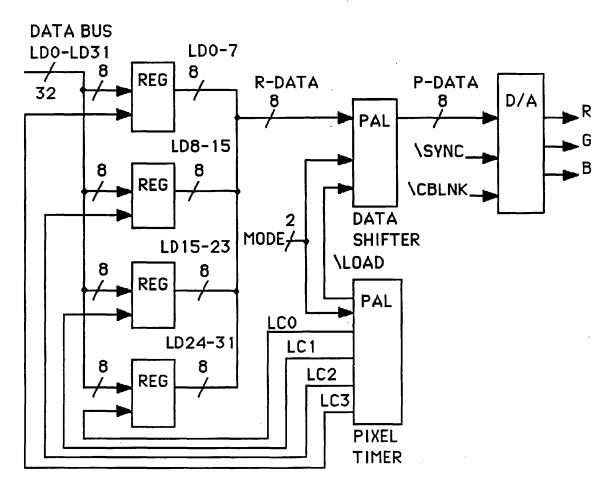

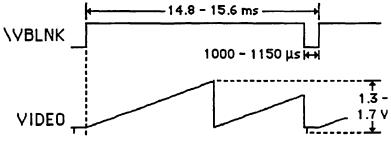

The vertical timing signals are generated in the same way. The vertical counters continually count up until reaching a count which causes the PAL to output a low level on the \VSET signal which reloads the counters. The vertical count represents the display line number. Lines 0-767 are visible lines. When the count reaches 768 the PAL outputs a low level on the \VBLNK (vertical blank) signal causing the video to be blanked. Three line counts later the \VSYNC (vertical sync) signal is driven low and ORed into the \SYNC signal triggering the monitor to begin the vertical retrace. The \VSYNC signal is low for three lines. The total \VBLNK interval is approximately one millisecond. Also within the \VBLNK period the \VSET signal is driven low causing the vertical counters to reload. When the count again reaches 0, the \VBLNK signal will go high for the beginning of the next video frame. The frame rate is determined by the line rate and the preset value of the vertical counters. The frame rate is 60Hz.

Figure 3-8 Vertical Timing Signals

Figure 3-9 Timing Generation Block Diagram

Other signals from the horizontal timing PAL are used to prevent the processor access to the video buffer during a TRANSFER cycle.

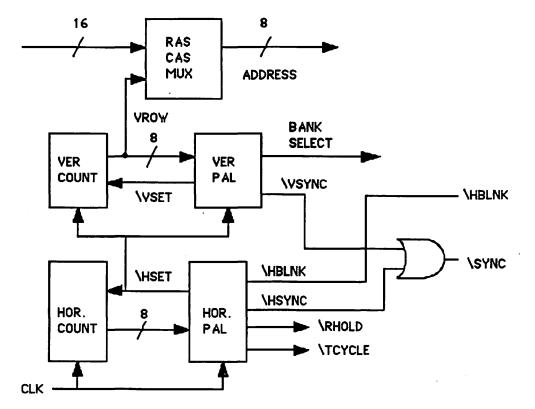

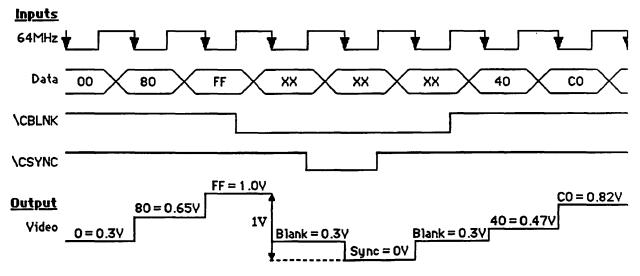

#### 3.3 RGB Video Output

To generate the actual analog video signals the RAM buffer is read out. There are four banks of RAM. Each bank is 1 out of every 4 pixels to the screen. In 8-bit mode the banks are read in an interleaved manner at up to 63 nanosecond cycle time for each bank which provides a pixel time of 16 nanoseconds. The data from the RAMs is converted to the proper format via U30, then sent into the VDAC (digital to analog) converter. The four VRAMs in each bank allow for 8 bits of information to be stored for each pixel. This allows 256 shades of red, green, blue, or some combination to be displayed; there is a possibility of over 16.7 million different colors. The video D/A converters also receive the \CBLNK and \SYNC signals. When both the blanking and sync signals are high the D/A's sample the digital data on the rising edge of the clock, and convert the digital RAM data into analog voltages. A data value of white will result in a voltage out of the D/A of approximately one volt which represents the brightest video level. Conversely a value of black will result in a voltage level of 0.3 volts. The \CBLNK signal also causes a black level to be output, and the \SYNC signal causes a voltage of zero volts to be output. The three video signals, one each representing red, green and blue, are separately transmitted to the video monitor. The \SYNC signal is also sent to the monitor independently at TTL voltage levels.

The R-data, as shown in Figure 3-10 Video Generation Block Diagram, is valid as follows: when LC0 is low, LD0-LD7 is valid; when LC1 is low, LD8-LD15 is valid; when LC2 is low, LD16-LD23 is valid; when LC 3 is low, LD24-LD31 is valid. When \LOAD is low, P-data is valid and when \LOAD is high, R-data is being shifted (reformatted) into a valid configuration.

Figure 3-10 Video Generation Block Diagram

The following diagram illustrates the operation of a video D/A. In practice the blanking and sync intervals will be longer.

Figure 3-11 Video D/A Operation

8/15/89

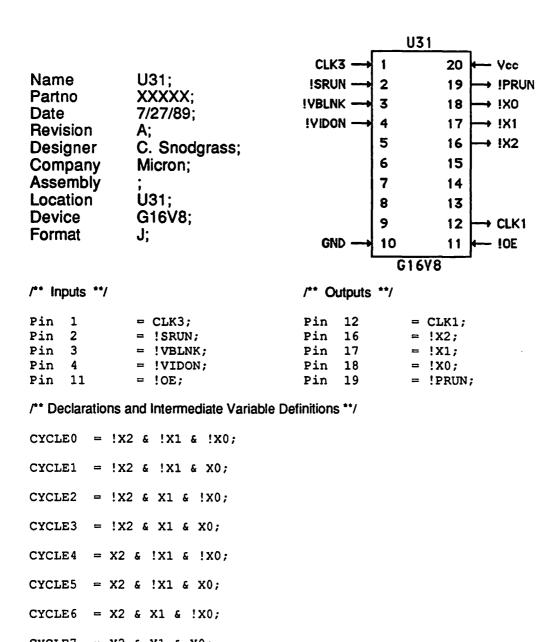

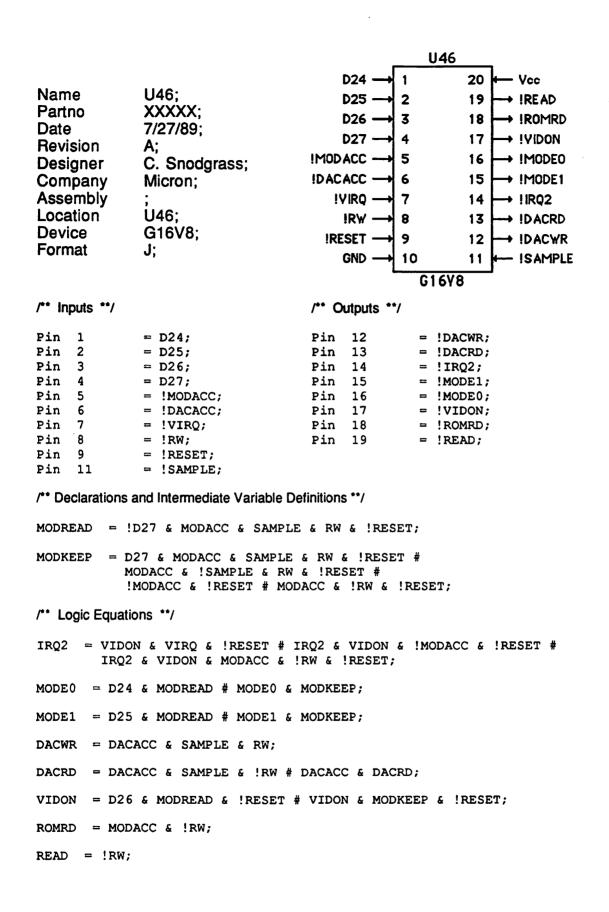

## Chapter 4 **PAL Description**

The Micron EXCEED SE/3010-78 Video Board contains ten 20-pin and 24-pin PALs. The boolean logic symbols are shown below:

| &<br>#                                                     | and<br>Or     | <pre>\$ EXCLUSIVE ! NOT or logic</pre> | OR<br>al INVERSION |  |

|------------------------------------------------------------|---------------|----------------------------------------|--------------------|--|

|                                                            |               | U1                                     |                    |  |

|                                                            |               |                                        | 20 + Vcc           |  |

| Name                                                       | U1;           |                                        | 19 - ILOAD         |  |

| Partno                                                     | XXXXX;        |                                        |                    |  |

| Date                                                       | 7/27/89;      |                                        |                    |  |

| Revision                                                   | A;            |                                        |                    |  |

| Designer                                                   | C. Snodgrass; | IXO → 5 1                              |                    |  |

| Company                                                    | Micron;       | !X1 <b>── </b> 6 1                     |                    |  |

| Assembly                                                   | •             | !X2 → 7 1                              | 4                  |  |

| Location                                                   | U1;           | 8 1                                    |                    |  |

| Device                                                     | G16V8;        |                                        |                    |  |

| Format                                                     | J;            |                                        |                    |  |

|                                                            |               |                                        | 1 • !OE            |  |

|                                                            |               | G16V8                                  |                    |  |

| /** Inputs **/                                             |               | /** Outputs **/                        |                    |  |

| Pin 1                                                      | = $CLK3;$     | Pin 12 = !LC:                          | 3;                 |  |

| Pin 2                                                      | = !MODE0;     | Pin 13 = !LC:                          | 2;                 |  |

| Pin 3                                                      | = !MODE1;     | Pin 14 = !LC:                          |                    |  |

| Pin 4                                                      | = !PRUN;      | Pin 15 = !LC                           |                    |  |

| Pin 5                                                      | = !X0;        | Pin 16 = !DRI                          | -                  |  |

| Pin 6                                                      | = !X1;        | Pin 17 = !TOC                          |                    |  |

| Pin 7                                                      | = ! X2 ;      | Pin 18 = !BLI                          |                    |  |

| Pin 11                                                     | = !OE;        | Pin 19 = !LO                           | AD;                |  |

| /** Declarations and Intermediate Variable Definitions **/ |               |                                        |                    |  |

CYCLE0 = !X2 & !X1 & !X0;CYCLE1 = !X2 & !X1 & X0;CYCLE2 = !X2 & X1 & !X0; CYCLE3 = !X2 & X1 & X0;CYCLE4 = X2 & !X1 & !X0;CYCLE5 = X2 & !X1 & X0;CYCLE6 = X2 & X1 & !X0;CYCLE7 = X2 & X1 & X0;

8/15/89

- M8BIT = MODE0 & MODE1;

- M4BIT = !MODE0 & MODE1;

- M2BIT = MODE0 & !MODE1;

- M1BIT = !MODE0 & !MODE1;

- /\*\* Logic Equations \*\*/

- LCO.D = PRUN & LCO & !TOGGLE & DRUN # PRUN & LC1 & TOGGLE # PRUN & !DRUN & CYCLE 3 # PRUN & !DRUN & CYCLE7;

- LC1.D = PRUN & LC1 & !TOGGLE & DRUN # PRUN & LC2 & TOGGLE # PRUN & !DRUN & CYCLE 2 # PRUN & !DRUN & CYCLE6;

- LC2.D = PRUN & LC2 & !TOGGLE & DRUN # PRUN & LC3 & TOGGLE # PRUN & !DRUN & CYCLE1 # PRUN & !DRUN & CYCLE5;

- LC3.D = PRUN & LC3 & !TOGGLE & DRUN # PRUN & LC0 & TOGGLE # PRUN & !DRUN & CYCLE0 # PRUN & !DRUN & CYCLE4;

- DRUN.D = PRUN & CYCLE7 # DRUN & PRUN;

- TOGGLE.D = PRUN & CYCLE7 # DRUN & M2BIT & CYCLE3 # DRUN & M4BIT & CYCLE1 # DRUN & M4BIT & CYCLE3 # DRUN & M4BIT & CYCLE5 # DRUN & M8BIT;

- !BLNK.D = DRUN & CYCLE1 # !BLNK & DRUN;

- LOAD.D = DRUN & M1BIT & CYCLE0 # DRUN & M2BIT & CYCLE0 # DRUN & M2BIT & CYCLE4 # DRUN & M4BIT & CYCLE0 # DRUN & M4BIT & CYCLE2 # DRUN & M4BIT & CYCLE4 # DRUN & M4BIT & CYCLE6 # DRUN & M8BIT;

| Name<br>Partno<br>Date<br>Revision<br>Designer<br>Company<br>Assembly<br>Location<br>Device<br>Format | U30;<br>XXXXX;<br>7/27/89;<br>A;<br>C. Snodgrass;<br>Micron;<br>;<br>U30;<br>G20V8;<br>J;                                                                                                                                                                                                                             | $CLK2 \longrightarrow 1$ $ SD0 \longrightarrow 2$ $ SD1 \longrightarrow 3$ $ SD2 \longrightarrow 4$ $ SD3 \longrightarrow 5$ $ SD4 \longrightarrow 6$ $ SD5 \longrightarrow 7$ $ SD6 \longrightarrow 8$ $ SD7 \longrightarrow 9$ $ MODE0 \longrightarrow 10$ $ MODE1 \longrightarrow 11$ $GND \longrightarrow 12$ | U30<br>24 $\leftarrow$ Vcc<br>23<br>22 $\rightarrow$ !PD7<br>21 $\rightarrow$ !PD6<br>20 $\rightarrow$ !PD5<br>19 $\rightarrow$ !PD4<br>18 $\rightarrow$ !PD3<br>17 $\rightarrow$ !PD2<br>16 $\rightarrow$ !PD1<br>15 $\rightarrow$ !PD0<br>14 $\leftarrow$ !LOAD<br>13 $\leftarrow$ !OE |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /** Inputs **/                                                                                        |                                                                                                                                                                                                                                                                                                                       | /** Outputs **/                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |

| S4BIT = !LO.<br>S2BIT = !LO.<br>S1BIT = !LO.                                                          | <pre>= CLK2;<br/>= !SD0;<br/>= !SD1;<br/>= !SD1;<br/>= !SD2;<br/>= !SD3;<br/>= !SD4;<br/>= !SD5;<br/>= !SD6;<br/>= !SD7;<br/>= !MODE0;<br/>= !MODE1;<br/>= !OE;<br/>= !LOAD;<br/>and Intermediate Variable Def<br/>AD &amp; !MODE0 &amp; MODE1;<br/>AD &amp; MODE0 &amp; !MODE1;<br/>D &amp; MODE0 &amp; MODE1;</pre> |                                                                                                                                                                                                                                                                                                                   | <pre>= !PD0;<br/>= !PD1;<br/>= !PD2;<br/>= !PD3;<br/>= !PD4;<br/>= !PD5;<br/>= !PD6;<br/>= !PD7;</pre>                                                                                                                                                                                   |

L4BIT = LOAD & !MODE0 & MODE1;

L2BIT = LOAD & MODEO & !MODE1;

L1BIT = LOAD & !MODE0 & !MODE1;

/\*\* Logic Equations \*\*/

PD7.D = SD7 & L8BIT # SD3 & L4BIT # SD1 & L2BIT # SD0 & L1BIT;

.

8/15/89

| PD6.D | SDO &          | L8BIT # SD2 & L4BIT #<br>L2BIT # SD1 & L1BIT #<br>S1BIT;                          |

|-------|----------------|-----------------------------------------------------------------------------------|

| PD5.D | SD3 &          | L8BIT # SD1 & L4BIT #<br>L2BIT # SD2 & L1BIT #<br>S2BIT # PD6 & S1BIT;            |

| PD4.D | SD2 &          | L8BIT # SD0 & L4BIT #<br>L2BIT # SD3 & L1BIT #<br>S2BIT # PD5 & S1BIT;            |

| PD3.D | SD5 &<br>PD7 & | L8BIT # SD7 & L4BIT #<br>L2BIT # SD4 & L1BIT #<br>S4BIT # PD5 & S2BIT #<br>S1BIT; |

| PD2.D | SD4 &<br>PD6 & | L8BIT # SD6 & L4BIT #<br>L2BIT # SD5 & L1BIT #<br>S4BIT # PD4 & S2BIT #<br>S1BIT; |

| PD1.D | SD7 &<br>PD5 & | L8BIT # SD5 & L4BIT #<br>L2BIT # SD6 & L1BIT #<br>S4BIT # PD3 & S2BIT #<br>S1BIT; |

| PD0.D | SD6 &          | S4BIT # PD2 & S2BIT #                                                             |

•

CYCLE7 = X2 & X1 & X0;

/\*\* Logic Equations \*\*/

PRUN.D = VIDON & VBLNK & SRUN & CLK1 # PRUN & SRUN # PRUN & CLK1;

X2.D = PRUN & CYCLE 3 # PRUN & CYCLE4 # PRUN & CYCLE5 # PRUN & CYCLE6;

X1.D = PRUN & CYCLE1 # PRUN & CYCLE2 & PRUN & CYCLE5 # PRUN & CYCLE6; X0.D = PRUN & CYCLE0 # PRUN & CYCLE2 # PRUN & CYCLE4 # PRUN & CYCLE6; CLK1.D = !CLK1;

SE/3010-78

24

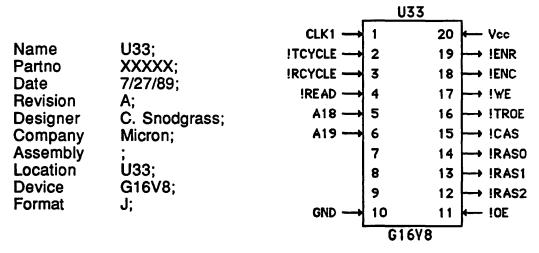

| /** |     |      | **/ |

|-----|-----|------|-----|

| /** | Inp | uis. |     |

/\*\* Outputs \*\*/

| Pin | 1  | = CLK1; | Pin     | 12 | =          | !RAS2; |

|-----|----|---------|---------|----|------------|--------|

| Pin | 2  | = !TCYC | LE; Pin | 13 | =          | !RAS1; |

| Pin | 3  | = !RCYC | LE; Pin | 14 | =          | !RAS0; |

| Pin | 4  | = !READ | ; Pin   | 15 | =          | !CAS;  |

| Pin | 5  | = A18;  | Pin     | 16 | <b>1</b> 2 | !TROE; |

| Pin | 6  | = A19;  | Pin     | 17 | =          | !WE;   |

| Pin | 11 | = !OE;  | Pin     | 18 | =          | !ENC;  |

|     |    |         | Pin     | 19 | E          | !ENR;  |

/\*\* Declarations and Intermediate Variable Definitions \*\*/

/\*\* Logic Equations \*\*/

TROE.D = RCYCLE & RAS0 & READ # RCYCLE & RAS1 & READ # RCYCLE & RAS2 & READ # TCYCLE & !CAS # TCYCLE & ENC;

CAS.D = ENC # CAS & RCYCLE # CAS & TCYCLE;

RASO.D = RCYCLE & !A18 & !A19 # TCYCLE & TROE # RASO & TCYCLE;

RAS1.D = RCYCLE & A18 & !A19 # TCYCLE & TROE # RAS1 & TCYCLE;

RAS2.D = RCYCLE & !A18 & A19 # TCYCLE & TROE # RAS2 & TCYCLE;

WE.D = !READ & RCYCLE & ENC # WE & RCYCLE;

ENC.D = RASO & !CAS & RCYCLE # RASO & !CAS & TCYCLE # RAS1 & !CAS & RCYCLE # RAS1 & !CAS & TCYCLE # RAS2 & !CAS & RCYCLE # RAS2 & !CAS & TCYCLE;

ENR.D = !RAS0 & !RAS1 & !RAS2 # CAS

8/15/89

|                  |                |             | <u> </u> | 6         |         |

|------------------|----------------|-------------|----------|-----------|---------|

|                  |                |             | 1        | 20        | ← Vcc   |

| Name             | U36;           |             | 2        | 19        |         |

| Partno           | XXXXX;         |             | 3        | 18        | → ISYNC |

| Date<br>Revision | 7/27/89;<br>A; | !HSYNC →    | 4        | 17        |         |

| Designer         | C. Snodgrass;  |             | 5        | 16        | → !₩EO  |

| Company          | Micron;        | !₩E•        | 6        | 15        | → !₩E1  |

| Assembly         | •              | sizo 🛶      | 7        | 14        | → !¥E2  |

| Location         | U36;           | SIZ1 →      | 8        | 13        | → !₩E3  |

| Device           | G16V8;         | BAO         | 9        | 12        |         |

| Format           | J;             | GND —→      | 10       | 11        | BA1     |

|                  |                | · · · · · · | G16      | <u>78</u> | ļ       |

/\*\* Inputs \*\*/

/\*\* Outputs \*\*/

| Pin | 4  | = !HSYNC; | Pin | 13 | = !WE3;  |

|-----|----|-----------|-----|----|----------|

| Pin | 5  | = !VSYNC; | Pin | 14 | = !WE2;  |

| Pin | 6  | = !WE;    | Pin | 15 | = !WE1;  |

| Pin | 7  | = SIZO;   | Pin | 16 | = !WE0;  |

| Pin | 8  | = SIZ1;   | Pin | 18 | = !SYNC; |

| Pin | 9  | = BA0;    |     |    |          |

| Pin | 11 | = BA1;    |     |    |          |

/\*\* Declarations and Intermediate Variable Definitions \*\*/

/\*\* Logic Equations \*\*/

WE3 = WE & !BA0 & !BA1;

WE2 = WE & BA0 & !BA1 # WE & !BA1 & !SIZO # WE & !BA1 & SIZ1;

WE1 = WE & !BA0 & BA1 # WE & !BA1 & !SIZ0 & !SIZ1 # WE & !BA1 & SIZ0 & SIZ1 # WE & !BA1 & BA0 & !SIZ0;

WE0 = WE & BA0 & BA1 # WE & BA0 & SIZO & SIZ1 # WE & !SIZO & !SIZ1 # WE & BA1 & SIZ1;

SYNC = VSYNC # HSYNC;

| Name<br>Partno<br>Date<br>Revision<br>Designer<br>Company<br>Assembly<br>Location<br>Device<br>Format | U39;<br>XXXXX;<br>7/27/89;<br>A;<br>C. Snodgrass;<br>Micron;<br>;<br>U39;<br>P20X8;<br>J;                                            | $U3$ $ HSET \rightarrow 1$ $ CR7 \rightarrow 2$ $3$ $R0 \rightarrow 4$ $R1 \rightarrow 5$ $R2 \rightarrow 6$ $R3 \rightarrow 7$ $R4 \rightarrow 8$ $R5 \rightarrow 9$ $R6 \rightarrow 10$ $R7 \rightarrow 11$ $GND \rightarrow 12$ $P20$ | $24 \leftarrow Vcc$ $23 \rightarrow !VIRQ$ $22 \rightarrow !VSET$ $21 \rightarrow !SEL0$ $20 \rightarrow !SEL1$ $19 \rightarrow !SEL2$ $18 \rightarrow !R8$ $17 \rightarrow !R9$ $16 \rightarrow !VSYNC$ $15 \rightarrow !VBLNK$ $14 \rightarrow R7S$ $13 \leftarrow !OE$ |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /** Inputs **/                                                                                        |                                                                                                                                      | /** Outputs **/                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                           |

| Pin 1<br>Pin 2<br>Pin 4<br>Pin 5<br>Pin 6<br>Pin 7<br>Pin 8<br>Pin 9<br>Pin 10<br>Pin 11<br>Pin 13    | <pre>= !HSET;<br/>= !CR7;<br/>= R0;<br/>= R1;<br/>= R2;<br/>= R3;<br/>= R4;<br/>= R4;<br/>= R5;<br/>= R6;<br/>= R7;<br/>= !OE;</pre> | Pin       15       =         Pin       16       =         Pin       17       =         Pin       18       =         Pin       19       =                                                                                                 | <pre>!R8;<br/>!SEL2;<br/>!SEL1;<br/>!SEL0;<br/>!VSET;</pre>                                                                                                                                                                                                               |

| /** Declarations a                                                                                    | and Intermediate Variable De                                                                                                         | efinitions **/                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                           |

| COUNT255M =                                                                                           | R7 & R6 & R5 & R4 &                                                                                                                  | R3 & R2 & R1 & F                                                                                                                                                                                                                         | .0;                                                                                                                                                                                                                                                                       |

| COUNT255 =                                                                                            | !R9 & !R8 & R7 & R6 &                                                                                                                | R5 & R4 & R3 &                                                                                                                                                                                                                           | R2 & R1 & R0;                                                                                                                                                                                                                                                             |

| COUNT511 =                                                                                            | !R9 & R8 & R7 & R6 &                                                                                                                 | R5 & R4 & R3 & F                                                                                                                                                                                                                         | 2 & R1 & R0;                                                                                                                                                                                                                                                              |

| COUNT767 = 2                                                                                          | R9 & !R8 & R7 & R6 &                                                                                                                 | R5 & R4 & R3 & F                                                                                                                                                                                                                         | 2 & R1 & R0;                                                                                                                                                                                                                                                              |

| COUNT770 =                                                                                            | R9 & R8 & !R7 & !R6 &                                                                                                                | !R5 & !R4 & !R3                                                                                                                                                                                                                          | & !R2 & R1 & !R0;                                                                                                                                                                                                                                                         |

| COUNT773 =                                                                                            | R9 & R8 & !R7 & !R6 &                                                                                                                | !R5 & !R4 & !R3                                                                                                                                                                                                                          | & R2 & !R1 & R0;                                                                                                                                                                                                                                                          |

| COUNT798 =                                                                                            | R9 & R8 & !R7 & !R6 &                                                                                                                | !R5 & R4 & R3 &                                                                                                                                                                                                                          | R2 & R1 & !R0;                                                                                                                                                                                                                                                            |

| COUNT799 = 1                                                                                          | R9 & R8 & !R7 & !R6 &                                                                                                                | !R5 & R4 & R3 &                                                                                                                                                                                                                          | R2 & R1 & R0;                                                                                                                                                                                                                                                             |

| /** Logic Equation                                                                                    | ons **/                                                                                                                              |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                           |

|                                                                                                       | !CR7 # !R7 & CR7;<br>OUNT767 # VBLNK \$ COU                                                                                          | NT799;                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                           |

VSYNC.D = COUNT770 # VSYNC \$ COUNT773;

R9.D = COUNT511 # R9 \$ COUNT799;

R8.D = COUNT255M # R8 \$ COUNT511 # COUNT799;

SEL2.D = COUNT511 # SEL2 \$ COUNT767;

SEL1.D = COUNT255 # SEL1 \$ COUNT511;

SEL0.D = COUNT799 # SEL0 \$ COUNT255;

VSET.D = COUNT798;

VIRQ = COUNT767;

/\*\* Declarations and Intermediate Variable Definitions \*\*/

= !OE;

COUNT14 = !C9 & !C8 & !C7 & !C6 & !C5 & !C4 & C3 & C2 & C1 & !C0;COUNT16M = !C9 & !C8 & !C7 & !C6 & !C5 & C4 & !C3;COUNT32M = !C9 & !C8 & !C7 & !C6 & C5 & !C4 & !C3;COUNT40 = !C9 & !C8 & !C7 & !C6 & C5 & !C4 & C3 & !C2 & !C1 & !C0;COUNT45 = !C9 & !C8 & !C7 & !C6 & C5 & !C4 & C3 & C2 & !C1 & C0;COUNT46 = !C9 & !C8 & !C7 & !C6 & C5 & !C4 & C3 & C2 & !C1 & C0;COUNT46 = !C9 & !C8 & !C7 & !C6 & C5 & !C4 & C3 & C2 & C1 & !C0;COUNT104 = !C9 & !C8 & !C7 & C6 & C5 & !C4 & C3 & !C2 & !C1 & !C0;COUNT255M = C7 & C6 & C5 & C4 & C3 & C2 & C1 & C0;COUNT511 = !C9 & C8 & C7 & C6 & C5 & !C4 & C3 & C2 & C1 & C0;COUNT620 = C9 & !C8 & !C7 & C6 & C5 & !C4 & C3 & C2 & C1 & !C0;COUNT662 = C9 & !C8 & C7 & !C6 & !C5 & C4 & :C5 & C4 & C3 & C2 & C1 & !C0;COUNT665 = C9 & !C8 & C7 & !C6 & !C5 & C4 & C3 & C2 & C4 & C3 & C2 & C1 & C0;

8/15/89

Pin

13

COUNT666 = C9 & !C8 & C7 & !C6 & !C5 & C4 & C3 & !C2 & C1 & !C0; COUNT768 = C9 & C8 & !C7 & !C6 & !C5 & !C4 & !C3 & !C2 & !C1 & !C0; /\* Logic Equations \*\*/ CR7.D = COUNT16M; RENAB.D = COUNT40 # RENAB \$ COUNT14; SRUN.D = COUNT104 # SRUN \$ COUNT620; TCYCLE.D = COUNT16M # COUNT32M; C9.D = COUNT511 # C9 \$ COUNT666 # COUNT768; C8.D = COUNT55M # C8 \$ COUNT511 # COUNT768; HSYNC.D = COUNT662 # HSYNC \$ COUNT46; RHOLD.D = COUNT666 # RHOLD \$ COUNT45; HSET.D = COUNT665;

|                |                |              | <u>U47</u> |    | _      |

|----------------|----------------|--------------|------------|----|--------|

|                |                |              | 1          | 20 | + Vcc  |

| Name           | U47;           | !STRMCLOCK → | 2          | 19 |        |

| Partno<br>Date | XXXXX;         | !RESET →     | 3          | 18 |        |

| Revision       | 7/27/89;<br>A; | !RAMACC →    | 4          | 17 |        |

| Designer       | C. Snodgrass;  | IANYACC      | 5          | 16 | → !ST4 |

| Company        | Micron;        | !Rhold →     | 6          | 15 | → IST3 |

| Assembly       | ;              | !srun →      | 7          | 14 | → !ST2 |

| Location       | U47;           | IDACACC →    | 8          | 13 | → IST1 |

| Device         | G16V8;         |              | 9          | 12 |        |

| Format         | J;             | GND →        | 10         | 11 | - !OE  |

|                |                |              | GIGYE      | 3  | -      |

/\*\* Inputs \*\*/

/\*\* Outputs \*\*/

| Pin | 1  | = CPUCLOCK;   | Pin | 12 | = !STRM;   |

|-----|----|---------------|-----|----|------------|

| Pin | 2  | = !STRMCLOCK; | Pin | 13 | = !ST1;    |

| Pin | 3  | = !RESET;     | Pin | 14 | = !ST2;    |

| Pin | 4  | = !RAMACC;    | Pin | 15 | = !ST3;    |

| Pin | 5  | = !ANYACC;    | Pin | 16 | = !ST4;    |

| Pin | 6  | = !RHOLD;     | Pin | 17 | = !RCYCLE; |

| Pin | 7  | = !SRUN;      | Pin | 18 | = !SAMPLE; |

| Pin | 8  | = !DACACC;    |     |    |            |

| Pin | 11 | = !OE;        |     |    |            |

/\*\* Declarations and Intermediate Variable Definitions \*\*/

ACCESS = ANYACC & !RESET;

COUNT0 = !ST4 & !ST3 & !ST2;

COUNT1 = !ST4 & !ST3 & ST2;

COUNT2 = !ST4 & ST3 & ST2;

COUNT3 = !ST4 & ST3 & !ST2;

COUNT4 = ST4 & ST3 & !ST2;

COUNT5 = ST4 & ST3 & ST2;

COUNT6 = ST4 & !ST3 & ST2;

/\*\* Logic Equations \*\*/

STRM = COUNT4 & STRMCLOCK # COUNT4 & STRM # COUNT5 & !STRMCLOCK;

STRM.OE = ACCESS;

ST2.D = ST1 & COUNT0 # COUNT1 # COUNT4 # COUNT5

ST3.D = COUNT1 # COUNT2 # COUNT3 # COUNT4;

ST4.D = COUNT3 # COUNT4 # COUNT5;

RCYCLE.D = RAMACC & ST1 & !RESET # RCYCLE & COUNT1 & !RESET #RCYCLE & COUNT2 & !RESET # RCYCLE & COUNT3 & !RESET # RCYCLE & COUNT4 & !RESET;

.

SAMPLE.D = ST1 # COUNT1;

| Name<br>Partno<br>Date<br>Revision<br>Designer<br>Company<br>Assembly<br>Location<br>Device<br>Format | U51;<br>XXXXX;<br>7/27/89;<br>A;<br>C. Snodgrass;<br>Micron;<br>;<br>U51;<br>G16V8;<br>J;                                                                                                                            | $A17 \rightarrow 1$ $A18 \rightarrow 2$ $A19 \rightarrow 3$ $A24 \rightarrow 4$ $A25 \rightarrow 5$ $A26 \rightarrow 6$ $A27 \rightarrow 7$ $A28 \rightarrow 8$ $A29 \rightarrow 9$ $GND \rightarrow 10$ $G10$ | $20 \leftarrow Vcc$ $19 \rightarrow IMODACC$ $18 \rightarrow IRAMACC$ $17 \rightarrow IANYACC$ $16 \leftarrow IAS$ $15 \leftarrow FCO$ $14 \leftarrow FC1$ $13 \leftarrow A31$ $12 \rightarrow IDACACC$ $11 \leftarrow A30$ |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| /** Inputs **/                                                                                        |                                                                                                                                                                                                                      | /** Outputs **/                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

|                                                                                                       | <pre>= A17;<br/>= A18;<br/>= A19;<br/>= A24;<br/>= A25;<br/>= A26;<br/>= A27;<br/>= A28;<br/>= A29;<br/>= A30;<br/>= A31;<br/>= FC1;<br/>= FC0;<br/>= !AS;<br/>and Intermediate Variable<br/># !A18 &amp; A19;</pre> | Pin 12<br>Pin 17<br>Pin 18<br>Pin 19<br>Definitions **/                                                                                                                                                        | <pre>= !DACACC;<br/>= !ANYACC;<br/>= !RAMACC;<br/>= !MODACC;</pre>                                                                                                                                                          |  |  |

| AMOD = A17                                                                                            |                                                                                                                                                                                                                      |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

|                                                                                                       | AMOD = A17 & A18 & A19;<br>ADAC = !A17 & A18 & A19;                                                                                                                                                                  |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

|                                                                                                       |                                                                                                                                                                                                                      |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

|                                                                                                       | AFA = !A24 & A25 & !A26 & A27 & A28 & A29 & A30 & A31 & AS;                                                                                                                                                          |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

|                                                                                                       | A29 & !A30 & A31 &                                                                                                                                                                                                   | AS;                                                                                                                                                                                                            |                                                                                                                                                                                                                             |  |  |

| /** Logic Equat                                                                                       | ions **/                                                                                                                                                                                                             |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

| RAMACC = ARAM & AFA # ARAM & AA;                                                                      |                                                                                                                                                                                                                      |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

| MODACC = AI                                                                                           | MODACC = AMOD & AFA # AMOD & AA;                                                                                                                                                                                     |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

| DACACC = AI                                                                                           | DAC & AFA # ADAC & A                                                                                                                                                                                                 | A;                                                                                                                                                                                                             |                                                                                                                                                                                                                             |  |  |

|                                                                                                       | FA & !FCO # AFA & !FC<br>A & !FCO # AA & !FC1                                                                                                                                                                        |                                                                                                                                                                                                                |                                                                                                                                                                                                                             |  |  |

8/15/89

34

.

# Chapter 5 Parts List

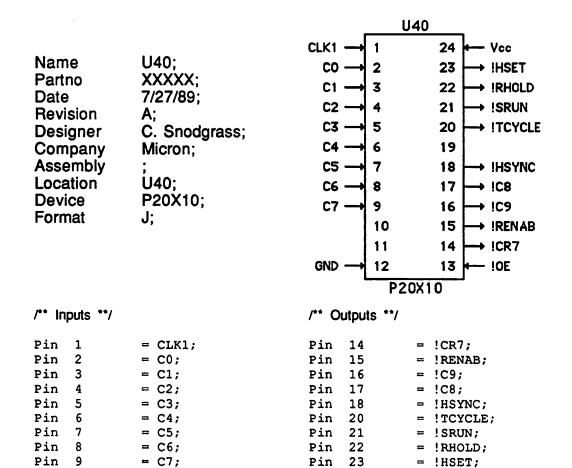

## Macintosh Video Board Parts List Xceed SE/3010-78 -- SE/30 8-Bit 1024 x 768

|            | Part                               | Micron    | # | Location         | Qty. |

|------------|------------------------------------|-----------|---|------------------|------|

| 1.         | GAL 16V8A-15                       | 71-07114  |   | U33,36,46,47,51  | 5    |

| 2.         | GAL 16V8A-10                       | 71-01305  |   | U1,31            | 2    |

| 3.         | GAL 20V8A-10                       | 71-01307  |   | <b>U</b> 30      | 1    |

| 4.         | TI PAL20X10-20CNT                  | 71-01311  |   | U40              | 1    |

| 5.         | TI PAL20X8-20CNT                   | 71-01301  |   | U39              | 1    |

| 6.         | IC, AMP AM29827                    | 71-012555 |   | U45,48           | 2    |

| 7.         | •                                  | 71-01316  |   | U32,35,38,41     | 4    |

| 8.         | IC, 74AS574N                       | 71-01322  |   | U2-4,29          | 4    |

| 9.         | IC, 74ALS645AN                     | 71-01303  |   | U49,50,52,53     | 4    |

| 10.        | IC, 74ALS869NT                     |           |   | U42,43           | 2    |

|            | IC, 74F241                         | 71-01324  |   | <b>U</b> 37      | 1    |

| 12.        | VRAM                               |           |   | U5-28            | 24   |

|            | Micron MT42C4064Z-15(-25)          |           |   |                  |      |

| 13.        | EPROM                              | 71-07106  |   | U44              | 1    |

|            | Signetics 27C32A-15FA              |           |   |                  |      |

| 14.        | VDAC                               | 71-07137  |   | U34              | 1    |

|            | Brooktree BT478KPJ66               |           |   |                  |      |

| 15.        | Oscillator, 64 MHz TTL             | 71-02042  |   | Yl               | 1    |

| 16.        | Diode, IN5908                      | 71-02035  |   | CR1              | 1    |

| 17.        | Voltage regulator                  | 71-07250  |   | <b>Z1</b>        | 1    |

|            | National LM385BZ-1.2               |           |   |                  |      |

|            | Capacitor, 0.1 uF, rad             | 72-CAP001 |   | C50-53           | 4    |

| 19.        | Capacitor, 0.1 uF                  | 71-04002  |   | all bypass,C1,C3 | 30   |

|            | 50V                                |           |   |                  |      |

| 20.        | Capacitor, tant, 33uF              | 71-04031  |   | C2,C4-6,C8       | 5    |

| _          | 10V AVX                            |           |   |                  |      |

| 21.        | Resistor, 147 ohm,                 | 71-03048  |   | R4               | 1    |

|            | 1/4 W 1%                           |           |   |                  |      |

| 22.        | Resistor, 1 Kohm,                  | 71-03020  |   | R5               | 1    |

|            | 1/4 W 5%                           |           |   | _                | _    |

| 23.        | Resistor, 75 ohm,                  | 71-03049  |   | R1-3             | .3   |

| <b>.</b> . | 1/4 W 1%                           |           |   |                  |      |

| 24.        | Resistor, SIP, 10-pin              | 71-03090  |   | RN8-11           | 4    |

|            | 2.2 Kohm                           |           |   |                  | _    |

| 25.        | Resistor, SIP, 10-pin              | 71-030915 |   | RN1-5            | 5    |

| 26         | 39 ohm                             | 71 07000  |   | * 1 10           | 10   |

| 20.        | Ferrite bead filter<br>#2743001112 | 71-07099  |   | L1-10            | 10   |

| 27         | #2743001112<br>Connector, 120-pin  | 72-001222 |   | 71               | 1    |

| 21.        | AMP 535022-1                       | 72-CON322 |   | J1               | Ŧ    |

| 20         | 10-pin connector                   | 71-07133  |   | J2               | 1    |

| 20.        | AMP 87631-6                        | /1-0/133  |   | 02               | 1    |

| 20         | Pin for 10-pin connector           | 72-001120 |   | cable            | 10   |

| 23.        | FIN TOT IN-DIN CONNECTOR           | 72-CON130 |   | Capte            | 10   |

8/15/89

|          |                          |           |          | - |

|----------|--------------------------|-----------|----------|---|

| 30.      | 10-pin connector plug    | 71-07109  | cable    | 1 |

|          | AMP 103168-3             |           |          |   |

| 31       | 15-pin D-shell connector | 71-07146  | cable    | 1 |

| J.       |                          | 12 01210  | 00510    | - |

|          | Vernitron 38-155         |           |          |   |

| 32.      | PCB                      |           | cable    | 1 |

| 33       | Mounting Bracket         | 71-07119  | cable    | 1 |

| <b>.</b> | -                        | 12 01225  | 00010    | - |

|          | AKB120                   |           |          |   |

| 34.      | Mounting hardware        |           |          |   |

| 35.      | Berg stick, 3-pin        | 71-020846 | IRE (J3) | 1 |

|          |                          |           | (00)     | - |

|          | 65500-203                |           |          |   |

| 36.      | Resistor, SIP, 10-pin    | 72-RES235 | RN6,7    | 2 |

|          | 270 ohm                  |           | ·        |   |

|          |                          |           |          |   |

## Chapter 6 Video Board Testing

## 6.1 General Test Flow

The video board must first be examined visually for any missing or wrong components, solder bridges, etc. A quick resistance test should find any power-to-ground shorts. There are three phases of the test: Initial, Burn-in, and Final. Initial Test checks to see that the board functions properly. Burn-in is an extended test. Final Test is a quick functionality test before the board is shipped.

Figure 6-1 Video Board Block Diagram

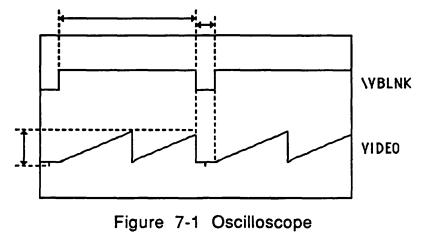

For the purposes of testing, Micron's Macintosh SE/30 8-Bit Video Board consists primarily of four elements: The bus interface, the VRAM array to store the pixel data, the ROM and control logic, and the D/A converter. The bus interface is essentially invisible. The VRAM array and ROM can be accessed at specific addresses in the memory map. The D/A converter's operation can best be verified by checking the screen for the proper patterns or looking at the video signals on an oscilloscope.

## 6.2 Test Specification

ECN.

# Chapter 7 Test Points/Oscilloscope

| Red                 | R3         | Pin 1 |

|---------------------|------------|-------|

| Red Return (ground) | R3         | Pin 2 |

| Green               | <b>R</b> 2 | Pin 1 |

| Green Return        | <b>R</b> 2 | Pin 2 |

| Blue                | <b>R1</b>  | Pin 1 |

| Blue Return         | <b>R1</b>  | Pin 2 |

## Appendix A Test Software

The test software is named '8Bit' and was written in-house. It may be modified as required. The following description covers the first release of the software, Version 1.00. On the Macintosh, software may be executed by doubleclicking with the mouse on the icon with the program name.

When the program begins execution, it creates a file named '0.txt.' The old '0.txt' file will be deleted. If the '0.txt' file exists and is open (if the computer crashed before closing the file), then the new file will be named '1.txt' or '2.txt' etc. Once the computer has been rebooted, the file names will begin over with '0.txt.'

The file created by the program is of type 'text.' Word-processing programs such as MacWrite and Word can convert the file to a readable form. If the file is to be printed, it should be converted to 9 point text in a font that allows the data to line up correctly, such as Monaco or Courier (laser font). This is done by selecting (highlighting) all of the text and choosing the size and font menu choices.

If there are no errors during the automatic tests, nothing will be printed into the file. Otherwise, the test types, patterns, and other test information is printed in the file along with any errors found. A '0' or '1' (zero or one) in a bit position means that the bit was correct; a '.' or '/' (period or slash) signifies a bit error. The burn-in test stops testing a board once too many errors have been found.

| expected | received | code |

|----------|----------|------|

| 0        | 0        | 0    |

| 0        | 1        |      |

| 1        | 0        | 1    |

| 1        | 1        | 1    |

Table A-1 File Error Output

Initial Test, Burn-in, and Final Test are included as options in the main menu. These tests are used during the normal test flow. If the board fails any of the tests, then any part of the test may be run separately for debugging purposes. The remainder of the menu options allow the individual tests to be run.

The automatic tests may be halted at any point by holding down the mouse button. The program will complete the current loop and return to the main menu. The VRAM tests and video patterns may also be halted in this manner.

When the test is started, it checks the computer's data for any boards that were found. The variables for the slot and address selections are set to the

first (or lowest number) board found. If the user enters addresses or slots for a board that is not in the system, the computer may crash when the software tries to write to invalid addresses. Never write to a slot that does not contain a board.

If the program did not find any Micron boards, it will put up a dialog asking which board is installed. The board should be found by the system, and if it is not then the test has failed. The test should only be used for debugging purposes if the board was not found.

### A.1 Test Options

To the right of the main window, there are several letters which represent the values of the test control flags. The flags control the general flow of the test: whether the data will be verified (checked for accuracy), whether information will be printed to the data file, etc. The setting of a flag is valid until it is either modified by the user's actions, or the test is halted. The automatic tests (initial, burn-in, final) may modify some of the flags. Flags may be changed through the 'Options' menu.

The flags that may be set by the user are listed below:

(H)elp will list information messages along with the menus as long as the flag is ON. Every menu selection changes the message written to the help window.

(V)erify ON will check the data that is read and print any errors to the file or screen if requested. If verify is OFF, then the data will not be checked.

(F)ile controls the test output. Errors will be printed into the file chosen by the user if the flag is ON.

(S)creen controls the test output to the screen. If the flag is OFF, most information will not be shown to the user.

The values (R)ead, (W)rite, and (.)Delay are set according to the 'Options' menu. They can not be individually changed by the user except through the menu.

'Number' of errors can be set to any number 1-999. If errors are found, then they will be reported up to this number of errors. After the number has been reached, the test will skip a block of memory and continue testing in this manner over the memory range.

'Number' of iterations is in the same dialog as Errors. Enter '0' for infinite iterations.

There are some exceptions to the flag settings. The ROTATE test will do a read/write test regardless of the flags, only using the Verify flag to determine if the data will be checked. The ROM verification test always reads the data regardless of the read/write flags, but follows the verify flag.

## A.2 VRAM Tests

The VRAM tests are solid, increment, random, and rotate. The options include read/write, addressing, pattern selection, and iterations. Holding the mouse button down at any time during the test will terminate it.

Selecting the read/write option will run a loop where the data is written to each address and then immediately read back. If the delay is used, then the data is written to the entire board before being read. The rotate test is automatically a read/write selection but does not change those flags.

The first address is the address at which the test will start. The test will run until it hits the address just below the last address entered. For example, running a test from c0001000 to c0001001 is the same as c0001000 to c0001004. Both will only test the first address c0001000.

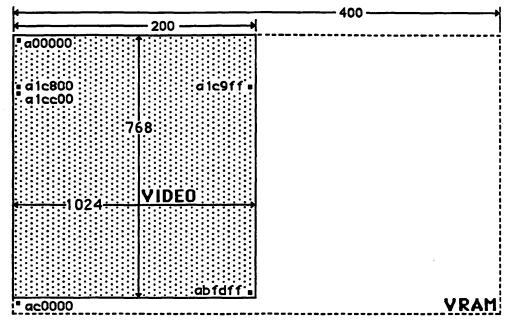

The VRAM tests should be used to test only the visible portion of the VRAM array, since the rest of the addresses do not affect the function of the board. The hex value for the distance across is used for this. Only 280 hex bytes are shown on the small screen; a total of 400 hex values exist per row. The large monitor shows all 400 hex bytes. The value in this variable selects the addresses in each row to test. (Note: The screen width 280 hex corresponds to 1024 pixels per row in decimal; 8-bit mode, one byte per pixel. For 4-bit mode one byte represents two pixels, or 140 hex bytes visible.)

Figure A-1 VRAM Array and Video Output: 8-Bit 1024x768

Figure A-2 VRAM Array and Video Output: 4-Bit 1024x768

The Solid test uses a single value for the data, entered by the user. The Increment test starts with the user-selected pattern, but increments the data by 1 at every address. The Random data is generated from a number selected by the user, and repeats every 4000 hex. Rotate uses its own data -- the value 111111 hex (1 hex = 0001 binary) is used, then 222222 (0010), 444444 (0100), and 888888 (1000) are written and read at a single address. The test begins at the next address with 111111 again. Rotate is a read/write test only.

All of the tests except Rotate allow the user to enter a starting value of one hex byte. All of the tests do not use bytes, though. Solid and Increment use byte values, Rotate uses words, and Random uses long words (8, 16, and 32 bits respectively).

#### A.3 Video Tests

The Video tests in the Miscellaneous menu are Color, Text, and Border. None of the video test data is verified. The important thing to note about the video patterns is if there are any pixels missing or if the pattern or colors are shown incorrectly.

The 'Color' test changes the color palette. A window is opened with blocks of different colors. The colors usually are different shades next to each other -- they should vary smoothly. If one of the colors doesn't match, the visual verification has failed.

The Text and Border tests put windows on the test screen. The alphabet is printed in several different sizes and fonts of text; it all should all be readable

in the text window. The Border test should show a white border around the edge of the screen, with black in the center.

Windows may only be opened in active screens. When a board is first put in a slot or moved to a new slot, the computer must be told (using Direct Monitor in the Control Panel) that the board exists, and be rebooted. Otherwise the windows will not appear on the second screen. This is why all boards are tested in the same slot during Initial and Final tests.

#### A.4 Miscellaneous

The Miscellaneous menu also allows testing of the ROM and control logic. The ROM data is contained in the high byte of the upper 2000 hex memory locations in a slot. The data is aliased, so also appears at multiples of these addresses (Fs300000-FsFFFFC). The ROM contains the driver for the board and information on the board type. The data is read from the ROM in the ROM test; the verify flag determines whether the data will be checked. In the test the ROM is read from the bottom to the top of the last possible address space, starting at FsFFE000.

Mode changes the bits/pixel information for the board. For visual verification, there is a small window that shows the explicit color palette. It has 256 blocks of color. If the board is in 1-bit mode, all of the blocks will be black or white. For 2- and 4-bit mode, vertical stripes of 4 or 16 different colors will be seen in the window. In 8-bit mode, each block will be a different color for a total of 256 colors.

The switch option turns the video board of and on. The screen will flash when the switch selection is used. From software, the status of the board can be determined by the least significant bit (LSB) in the most significant byte of the VRAM data. This is NOT data actually stored in the VRAM array -- only the 3 bytes of data in the VRAMs are normally shown in the VRAM tests. If the board is on, this bit will be high; if the board is off the bit will be low. The switch test also requires user verification to be sure the board was turned off. There are several addresses that may be used to switch the board; they may be chosen as offsets from the board base address (200000-2FFFFC).

## Appendix B Schematics

| PIN | R0₩ C     | R0₩ B    | ROW A    |

|-----|-----------|----------|----------|

| 40  | +12       | -5       | -12      |

| 39  | GND       | GND      | GND      |

| 38  | C16M      | ECLK     | CPUclock |

| 37  | +5        | +5       | +5       |

| 36  | AO        | A1       | A2       |

| 35  | A3        | A4       | A5       |

| 34  | A6        | GND      | A7       |

| 33  | <b>A8</b> | A9       | A10      |

| 32  | A11       | A12      | A13      |

| 31  | A14       | +5       | A15      |

| 30  | A16       | A17      | A18      |

| 29  | A19       | A20      | A21      |

| 28  | A22       | GND      | A23      |

| 27  | A24       | A25      | A26      |

| 26  | A27       | A28      | A29      |

| 25  | A30       | +5       | A31      |

| 24  | D31       | D30      | D29      |

| 23  | D28       | D27      | D26      |

| 22  | D25       | GND      | D24      |