The Inside Story on the New RISC-Based Macintosh

# Power Shacintosh

B O O K

Stephan Somogyi

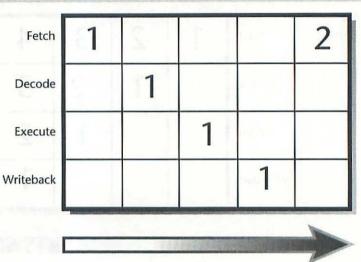

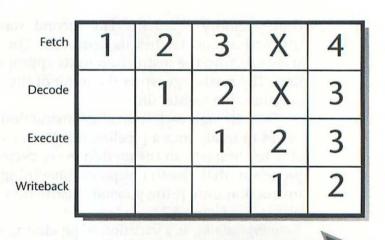

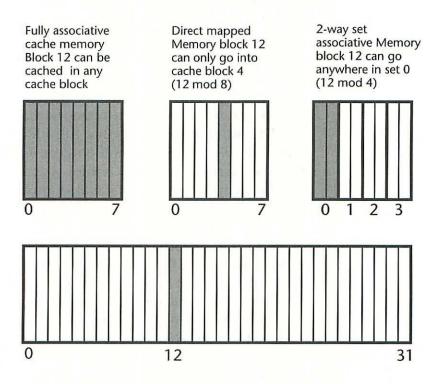

Foreword by Donald A. Norman

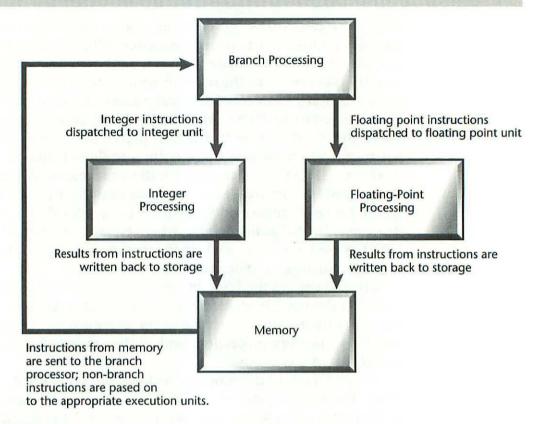

# The PowerPC™ Macintosh® Book

# The Inside Story on the New RISC-Based Macintosh

## Stephan Somogyi

Foreword by Donald A. Norman

Addison-Wesley Publishing Company

Reading, Massachusetts • Menlo Park, California • New York

Don Mills, Ontario • Wokingham, England • Amsterdam

Bonn • Sydney • Singapore • Tokyo • Madrid • San Juan

Paris • Seoul • Milan • Mexico City • Taipei

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters or all capital letters.

The authors and publishers have taken care in preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

#### Library of Congress Cataloging-in-Publication Data

Somogyi, Stephan.

The PowerPC Macintosh book / Stephan Somogyi

p. cm.

Includes index.

ISBN 0-201-62650-0

1. Macintosh (Computer) 2. RISC microprocessors.

II. Title.

QA76.8.M3S665 1994

004.165--dc20

93-38276 CIP

Copyright © 1994 by Stephan Somogyi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

Sponsoring Editor: David Clark

Project Manager: Joanne Clapp Fullagar

Production Coordinator: Gail McDonald Jordan

Cover design: Barbara T. Atkinson Text design: Joyce C. Weston

Set in 11 point Stone Sans by Shepherd, Inc.

1 2 3 4 5 6 7 8 9 -CRW- 9897969594 First printing, August 1994

Addison-Wesley books are available for bulk purchases by corporations, institutions, and other organizations. For more information please contact the Corporate, Government, and Special Sales Department at (800) 238-9682.

"...we shall never surrender."

—Sir Winston Churchill

# Contents

| Foreword     |                                                                                                                                                                        | xiii                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Introduction |                                                                                                                                                                        |                                                                      |

| Chapter 1    | How We Got Here From There                                                                                                                                             | 1                                                                    |

|              | RISC at Apple RISC for the Mainstream Deal of the Century RISC System Software Diversification How We Got Here From There                                              | 3<br>10<br>12<br>21<br>23<br>28                                      |

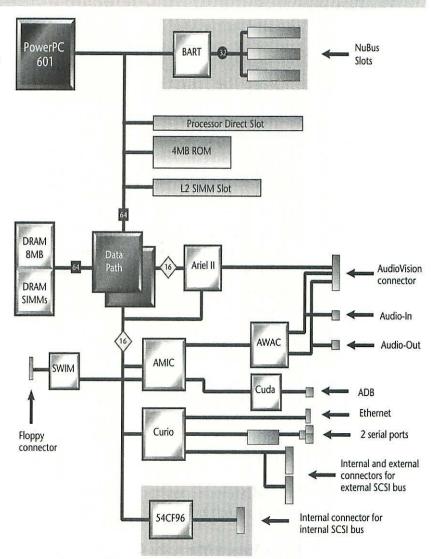

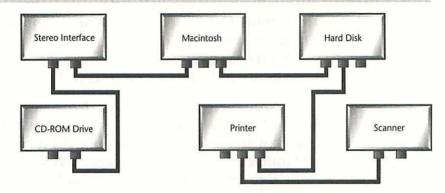

| Chapter 2    | Power Macintosh Hardware Overview                                                                                                                                      | 31                                                                   |

|              | The Big Picture The PowerPC 601 Direct Memory Access Memory Video Storage and SCSI NuBus GeoPort Ports Sound The Power Macintosh Upgrade Card ABS Hardware Performance | 32<br>33<br>36<br>37<br>41<br>46<br>51<br>52<br>52<br>53<br>53<br>55 |

| Chapter 3    | Power Macintosh Software Overview                                                                                                                                      | 57                                                                   |

|              | Power Macintosh System Software<br>Emulation                                                                                                                           | 57<br>60                                                             |

| vi The F  | PowerPC Macintosh                                                                                                                                                   |                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|           | Native PowerPC System Software Mixed Mode Native QuickDraw Native QuickTime Memory: Modern and Virtual Both I/O INITs and Patches Software on the Power Macintosh   | 61<br>62<br>66<br>68<br>69<br>71<br>73<br>82         |

| Chapter 4 | An Introduction to Microprocessors                                                                                                                                  | 85                                                   |

|           | Fundamental Microprocessor Concepts<br>Architecture<br>Implementation<br>Caches                                                                                     | 85<br>94<br>97<br>97                                 |

| Chapter 5 | The PowerPC Family                                                                                                                                                  | 103                                                  |

|           | Now We're Playing with POWER What Makes a PowerPC a PowerPC? The Abstract PowerPC The PowerPC 601 The PowerPC 603 The PowerPC 604 The PowerPC 403GA The PowerPC 620 | 103<br>107<br>109<br>112<br>120<br>127<br>132<br>134 |

| Chapter 6 | <b>Emulators on the Power Macintosh</b>                                                                                                                             | 137                                                  |

|           | Emulation Works The 68LC040 Emulator SoftWindows Wabi The Bottom Line                                                                                               | 138<br>138<br>148<br>153<br>157                      |

| Chapter 7 | Power Macintosh Hardware in Depth                                                                                                                                   | 159                                                  |

|           | System Hardware Upgrade Card                                                                                                                                        | 160<br>178                                           |

|            |                                                                                               | Contents | vii                             |

|------------|-----------------------------------------------------------------------------------------------|----------|---------------------------------|

|            | AV Card<br>VRAM Expansion Card                                                                |          | 179<br>182                      |

| Chapter 8  | Power Macintosh Software in Depth                                                             |          | 185                             |

|            | Mixed Mode<br>Call Chains<br>Extensions and Fat Patches<br>The Code Fragment Manager<br>Traps |          | 185<br>188<br>189<br>192<br>195 |

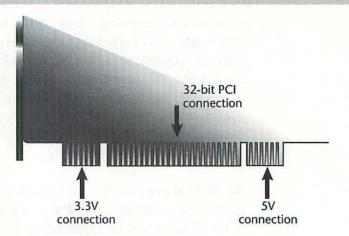

| Chapter 9  | Looking Ahead                                                                                 |          | 199                             |

|            | Hardware The PowerPC Reference Platform Graphing Calculator System Software The Future        |          | 200<br>206<br>209<br>210<br>214 |

| Appendix A | Resources                                                                                     |          | 217                             |

## **Thanks**

It is impossible for me to imagine what this book would be like without the extraordinary help of the following people. To claim that they have my heartfelt gratitude would be an understatement.

Jack McHenry, for helping in more ways than I can enumerate and for trusting me enough to let me camp out.

Tim Olson, for pitching in unhesitatingly when things were looking bleak and for providing the core content for Chapter 4.

Jim Gable, for taking the time to read the whole manuscript despite having more than enough other things to do, for the Sunday—night—at—10 phone conversations, and for being a staunch supporter throughout this endeavor.

Maggie Canon, *MacUser's* Editor-in-Chief, for giving me the freedom to get this book done.

Richard Zulch, co-conspirator, for being a high-fidelity sounding board.

Rik Myslewski, fellow raw fish addict of eastern European descent, for deconstruction services and reality checks.

Pam Pfiffner, my fearless leader at *MacUser*, for being quite the understanding boss.

Frank Casanova, for offering help when I needed it.

Richard Clark, for helping out despite maximum entropy in his own world.

# More Thanks

In the past, when I've read books that started with "Many people contributed to this book, without whom it wouldn't be nearly as good as it is," or something along those lines, I've dismissed such descriptions, as well as the number of people listed, as exaggerated.

Having finished this, my first book, I can say with some authority that they weren't kidding after all.

The people listed below contributed to this book in one way or another, but not by just "doing their job." They went out of their way to provide information, access, time out of their busy schedules, and other valuable resources when I needed them.

First of all, thanks to those who, among other things, took the time to read parts of this book, often in rather rough form, and provided much-needed feedback despite deadlines of their own: Keith Cox, Michael Dhuey, Bob Hollyer, Gary Kacmarcik, Alan Lillich, Zenon Kuc, Phil Koch, Paul Nixon, and Eric Traut. Any remaining errors are my fault, not theirs.

Thanks also to: Joseph Aseo, Ron Avitzur, Sam Barone, Sheila Brady, Pierre Césarini, Gary Davidian, Ross Ely, Jon Fitch, Don Fotsch, Bill Goins, Carl Hewitt, Ray Jaafari, Annette Machado, Bob Mansfield, Hugh Martin, Jordan Mattson, Brian Mellea, John Mitchell, Dean Mosley, John Nelson, Rolly Reed, Pete Richardson, Greg Robbins, John Sell, Betty Taylor, George Towner, Keri Walker, Gayle Ryan Westbrook, Jim Venable, Paul Wolf, and Mike Yamamura.

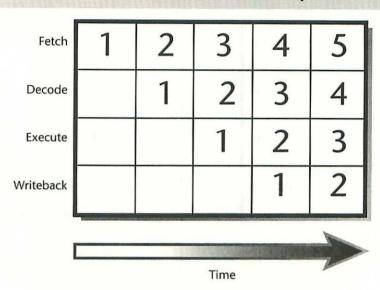

Special thanks go to John Hennessey and Dave Patterson, as well as the kind folks at Morgan Kaufman Publishers, who graciously allowed me to use the figure on page 99 from their book, *Computer Architecture: A Quantitive Approach*, which is listed in Appendix A.

My thanks go to Don Norman for agreeing to write the

foreword. His perspective is one that I wish more people in the high-technology industries would adopt.

Thanks also go to my friends in close proximity, who kept me reasonably sane while this thing took over my life for far too long: Nico Kamp & Katy McNamara, Mark Frost, Linda Pitcher, Levi Thomas & Larry Yaeger, and Mitch Ratcliffe.

I'd also like to thank the following people who had no direct input on the content of this book but provided greatly appreciated moral support by checking for life signs and making sure I hadn't imploded: David Biedny, Trudy Edelson, Devon Hubbard, Tom Nielsen, Leonard Rosenthol, and Rich Siegel.

Last but not least, thanks to Carole McClendon for handling the dickering early on, and to David Clark, Joanne Clapp Fullagar, Keith Wollman, and Steve Stansel at Addison-Wesley who thought this was a worthwhile undertaking, and to Gail McDonald Jordan for making it all come together in the end.

### **Foreword**

At first glance, I might seem to be a strange person to be writing the foreword to a book about the PowerPC Macintosh. Until 1993, I was a professor of cognitive science at the University of California, San Diego, a scientist who studied the human mind. Now that I'm at Apple, I serve several roles. As an Apple Fellow, I wander across company divisions as champion of the user. In AppleSoft, our software division, I operate under the title User Experience Architect. Neither of these roles would appear to have anything to do with a new piece of hardware, especially a CPU chip. What has this got to do with either human interface or user experience?

The exciting way to view the new chip is as an enabler for entirely new things that simply could not be imagined before. The PowerPC represents a completely new philosophy and style of CPU for personal computers, which provides entry to a whole new level of affordable performance. This powerful chip will allow users to discover totally new ways of working with machines.

Look, I don't believe the average citizen cares about the technical aspects of computing, such as:

- The operating system;

- · The kind of chip used for their CPU;

- · How much memory they have;

- CPU speed.

There are several ways to view the power of a CPU based on a reduced instruction set computer (RISC) architecture. One way is simply to look at the speed of the chip: It is incredibly fast. In that sense, the PowerPC is a supercharger. It makes the things we are already doing with computers go faster. That's neat, but it isn't the sort of thing that makes

most people's hearts beat faster. Will the average person appreciate that a word processor or spreadsheet is faster? I doubt it.

Many people are led to believe they should care about the technology, but that is only because of the way computers are currently marketed. Computer journalists, especially those who write for the trade magazines, tend to be champions of technology. They, and the salespeople in computer stores, emphasize the technology. But the average person doesn't really care about the details of technology. What we, the everyday users, really care about is getting on with our lives—enjoying our lives. Even the focus on making computers friendly is wrong because it still emphasizes the computer itself.

I care about getting something done: reading the latest news story; seeing the demo my colleague in Tokyo just filmed; learning how sales are doing with our new catalog services; making a reservation at that new restaurant (specifying no smoking, and maybe even peeking at the menu). I care about doing these things and preparing my material so that others can use it, but not about using a computer.

Until now, we have designed machines from the machine's point of view. Computers use information. Invisible. Arbitrary. Difficult. To work, they require precise syntax, details, logic— just the sort of things we are bad at. But there is a mismatch: People are perceptual devices, machines are symbolic.

If we want machines that are easy to use and comfortable for people, we have to make them match people's capabilities. We have to provide perceptual information and minimize the requirements for precise, numerical, or syntactically correct inputs. A graphical user interface such as the Macintosh desktop takes the first steps toward the solution by making heavy use of graphics and menus. But these are primitive steps. The desktop isn't really a desktop, and this graphical user interface isn't really very graphical. The visual

appearance is rather flat, more like line drawings and illustrations than rich, visual representations. Up to now, we have lacked the computer power necessary to do more. If we want machines to match people, we need to match the computing power of the brain, or at least of the eyes and ears. Then we can use more natural modes of interaction than keyboard and mouse and arbitrary commands. We can use speech, handwriting, gestures, and whatever else our creativity offers.

The brain is an incredibly powerful device, but it works very differently from our computers. Each element in the brain— the individual neuron—is fairly slow, noisy, and unreliable. It is a semidigital, semianalog device, capable of doing complex signal processing. But there are some  $10^{12}$  neurons, each making an average of  $10^4$  connections, so interconnected that the apparent slowness and lack of reliability of the individual neuron yields a fast, powerful, robust system. Each of the  $10^{16}$  connections transmits 10 to 100 impulses per second, for a total bandwidth of  $10^{17}$  to  $10^{18}$  impulses per second. The eyes alone generate about 200 megabits of data per second. The brain is a vast, parallel, neural computer that has very different properties from our serial, digital machines.

Computers are good at the stuff we find hard, and bad at the stuff we find easy, such as seeing and walking and talking and—well, all the stuff we all do so well that we take it for granted.

What are people good at? Creativity, humor, emotions, enjoyment. Sports, music, art. What are we bad at? Remembering details, systematic logic, arithmetic, spelling. What are computers good at? Details, systematic logic, arithmetic.

Now that we are moving to much more powerful CPUs, we can begin to make computers that interact with people on human terms. There are several ways in which this new power might be used. Let me point out some that might not

be obvious. Consider the conceptual model of a typical application. People are very good at understanding sensible, coherent structures and not so good at understanding or remembering arbitrary commands and actions. This is one of the powers of the graphical user interface over the command-line interface. The real trick in making computers understandable is to provide a coherent, intelligible conceptualization to the users, making sure that all operations and results conform. Today's graphical interfaces do not present a coherent conceptual model. The user may have no understanding of how or why operations get performed. In a spreadsheet, it is difficult to tell the ranges of the functions—just which cells are included in the operation. As a result, when you are using someone else's spreadsheet, it is often difficult to tell just what computations are being performed, and what values are relevant. In a database, it isn't always clear which individual records have been linked, or which operations any query might have to use. Relational databases are often difficult for people to set up and query. in part because they lack an intelligible conceptual model of the operations.

Now that we have the appropriate computer power, we could provide powerful clues to the underlying conceptual model through graphics. Imagine a database query that showed a pictorial rendition of the records and illustrated how a query traversed them, putting together the information for its response. A proper illustration would dramatically improve the user's understanding and make the debugging of failed queries or improperly constructed records much simpler.

Consider educational packages that can make much heavier use of simulation, showing in detail the underlying operations. Today, we have many simulation packages, but they mostly concentrate upon the outcome, not upon showing the underlying processes. Suppose we could illustrate the process as well as the outcome?

What about new methods of interaction, more effective modes? Say gesture, or speech, or handwriting? Or what about using three-dimensional graphics, sound, or speech output? For all of these, we require a lot more computing power. We require the PowerPC.

Today, the user does all the work. Do you want to send a file to a colleague over the network? You must know lots of technical details, including the network path and the name of your colleague's machine. You have to make sure the file and computer protections are appropriate. You have to know if your colleague has the correct applications and fonts. Suppose you could delegate all of this: "Send this OpenDoc document and viewer to Helen." Let the machine worry about the details, bothering you only if it isn't sure which Helen you had in mind or if a serious problem arises. This form of interaction—delegation rather than direct manipulation—requires some inference and general-purpose knowledge by the computer agent that is to do the task—more reason why we need the capability of the PowerPC.

The Power Macintosh provides a new hardware platform, but I think of it as a mere beginning, as an enabler. The truth is, I don't know what the future will bring; nobody ever does. The secret is to be able to take advantage of new potentials, to help us move to another, higher level of capability. This is where we stand today. This book sets the stage by giving you the details you need to take that step. The world of computing has had a prodigious set of advances in the previous ten years. We are now beginning an equally marvelous set of changes during the next decade.

Donald A. Norman Apple Fellow Apple Computer, Inc. Cupertino, California

# Introduction

A little more than 10 years ago, a group of stubborn people at Apple Computer shipped the Macintosh and introduced the personal-computing world to a slew of neat new stuff that few users at the time knew what to do with. Those few who "got it" were quickly branded zealots, dismissed as a fringe group, and deemed not part of the Serious Business Computing World.

During the intervening 10 years, the Macintosh has become a computer to be reckoned with in the business world, despite still owning less than 15 percent of the personal computer market. Imitation—litigation notwithstanding—is the sincerest form of flattery, and Windows is doing its best to catch up to the Mac operating system. One of the Mac's great hallmarks has been its integration of system software with hardware. The suggestion that Macintosh hardware is a copy-protection device for the Macintosh operating system has a kernel of truth to it: Apple's strategy has limited the Macintosh environment to its own hardware and, by doing so, limited the proliferation of the Mac but also kept a degree of consistency and compatibility between product generations that is unparalleled elsewhere.

The first generation of Power Macs is a bridge between the past and the upcoming decades. This first generation of Macs using the PowerPC 601 chip are real Macs; no compromises were made to provide extra performance at the expense of compatibility. The ongoing survival of the Macintosh, both hardware and software, depends on the success of these first Power Macs.

The first step in the migration allows Power Mac owners to run their existing Macintosh software, based on the Motorola 68000 (68k) chips on the new machines. Given the investment that current Mac users have in their software, without this compatibility, the Power Macs would be

non—starters. Fortunately, 68k compatibility isn't an issue, as the Power Macs' 68k emulator has already proven reliable, compatible, and adequately fast for most tasks.

The second part of the switchover from 68k to PowerPC is centered around native software that takes full advantage of the performance that the PowerPC-based systems are capable of.

#### What's in This Book

This book is structured to be read sequentially, but it can be used as a reference as well. Those reading it from start to finish will find it increases in technical depth as it progresses. It's designed to provide useful information to anyone interested in acquiring more than a superficial understanding of the first generation of Power Macs and the issues that surround them.

Chapter 1 sets the stage for the Power Macs by going over the history and development of the PowerPC alliance, a previously inconceivable coalition of former competitors. Chapters 2 and 3 provide an overview of the Power Macintosh hardware and software, to get you acquainted with the new machines from a big—picture perspective.

Chapter 4 is an introduction to microprocessors. Differentiation of personal computers today has become increasingly complex and subtle. The ability to distinguish disinformation from useful detail requires more than a cursory knowledge of how the chips work. This chapter offers a painless introduction to the key characteristics and differentiators of different microprocessors.

Chapter 5 introduces the known members of the PowerPC family of microprocessors. Even though the 601 is the only one shipping in systems as this book goes to press, much is already known about its siblings' capabilities.

Chapter 6 is first of the three Power Mac in-depth chapters; it explains the different emulators for the Power Mac

and how they work. Chapter 7 offers an in-depth look at the Power Mac hardware, and Chapter 8 does the same for Power Mac software.

Finally, Chapter 9 looks into the future at technologies that are relevant to the Power Macs or PowerPC-based personal computers in general. These first machines from Apple are only the beginning, and some of the future is already visible.

#### Who This Book Is For

This book is not a step-by-step guide to specific migration strategies. Its goal is to provide the necessary information to allow individuals(or organizations) to make educated decisions about when and how to migrate.

Those who wonder whether to switch to PowerPC now or wait for an even faster Power Mac are doomed to indecision. There will always be a newer, better, whizzier Power Mac just around the corner. The best method for deciding when to switch to the Power Macs is straightforward. Determine the amount of productivity gain you can get from a Power Mac now, and base your decision on that. Most computationally intensive software, especially graphics and desktoppublishing packages, are available now in native versions, optimized specifically for the Power Mac. If you spend most of your time waiting for your Macintosh to catch up, a Power Mac will almost certainly alleviate the problem. Those with compute-intensive software that requires a 68kbased Mac but that isn't yet available in a native version may want to hold off for a while. Bear in mind, though, that the future of Macintosh is PowerPC, the 68k-based Macs' days are numbered.

Users of x86-based PCs may also find this book useful in explaining the features of the new Macs. With the Power Macs, the price/performance ratio is in favor of the

Macintosh for the first time. Existing Windows users can even run most of their Windows applications on their Power Macs with the help of Insignia's SoftWindows.

#### **Now What**

I hope this book will get you started on your way into the world of Power Macintosh. The PowerPC alliance and the resultant microprocessors are pitted in head-to-head competition with Intel and its highest-end x86 processors. The Power PC offers the first viable alternative to the x86 because of the performance it offers at a comparatively low price. Although x86 PCs have always been able to offer greater performance for equal or less money, this is no longer the case.

In the long run, adoption of the PowerPC by systems vendors also heralds the beginning of operating system (OS) agnosticism. OSs will no longer be tied to the microprocessor families they run on. The Mac OS runs on 68k- and PowerPC-based systems, and Windows NT will be available for PowerPC machines, as will be some incarnations of IBM's OS/2 and AIX. Non-NT Windows is also available, with the help of SoftWindows, on non-x86 platforms.

The notion of functioning industry alliances is also becoming more accepted. The success of the PowerPC troika is a major counterbalance to the cynicism that developed after the vast number of failed collaborative in past years. The fact that three companies as different as Apple, IBM, and Motorola can work together speaks for the adage that where there is a will, there is a way.

So far, 1994 has seen great changes in the computer industry, and they show no sign of abating. Intel's dominance is being contested not only by PowerPC, but also on the x86 side by companies such as AMD and Cyrix, which are gaining influential allies among systems vendors.

The Power Macs are at the forefront of all this change, and Apple for the first time stands a good chance of gaining significant ground against the installed base of Intel-based Windows PCs.

Soon Macintosh systems will be developed that bring the PowerPC's performance across the entire Macintosh product line. With all these PowerPC-based Macs will come new software that takes full advantage of the available horsepower. Sometimes thereafter, we will no doubt wonder how we ever got along without Power Macs.

Stephan Somogyi San Francisco, California May 1994 Somogyi@ZIFF.COM

# How We Got Here from There

he Power Macintosh is a major leap forward in the evolution of the Macintosh.

In hindsight, the change in the Macintosh since its introduction in 1984 has been a gradual one. Memory capacity has grown from 128 kilobytes to hundreds of megabytes, storage capacity has gone from a 400-kilobyte floppy to multigigabyte hard drives, and increasingly powerful members of Motorola's 68000 (68k) processor family have become the engines driving an ever-increasing number of Macintosh computers. However, the performance of later 68k chips—the 68020, 68030, and 68040—didn't increase nearly as much as the capabilities of either memory or mass-storage technology.

Putting a completely different processor, a PowerPC chip, at the core of a Macintosh appears at first to be a profound change, one that makes a Mac not quite a Mac anymore. Far from it.

A Power Macintosh is a Macintosh—an extraordinarily fast one. A Power Macintosh can run all your existing Mac applications—with very few exceptions, thanks to sophisticated software technology—and with the System 7 user interface you're accustomed to. Almost any hardware that you can connect to a 68k-based Macintosh works with a

#### Jargon 101

RISC stands for reduced instruction-set computer. This term describes microprocessors that were developed with a specific design philosophy in mind. The basic idea is that a chip can perform many simple functions in the same time that a CISC chip can perform a single complex function.

RISC's conventional counterpart is CISC: complex instruction-set computer. CISC chips distinguish themselves by performing more complex functions, but with a comparatively steep performance penalty compared to RISC. CISC chips generally perform more slowly, are more complicated to design and manufacture, and are consequently more expensive. The latest CISC chips, such as Intel's Pentium, have many RISC-like features but aren't really RISC chips; they must still perform complex functions like their predecessors for compatibility reasons.

The term *architecture* is used to describe the basic design features that different chips of a processor family have in common, such as number of registers, floating-point capabilities, memory management, and the like. PowerPC is an architecture whose family initially contains the 601, 603, 604, and 620 chips.

POWER, the name of IBM's RISC architecture that was the basis for PowerPC, is another one of those great computer acronyms that itself contains an acronym: performance optimized with enhanced RISC.

If you want more details about microprocessor basics, the chips and features of the PowerPC family, and other chips that are competing with PowerPC, see Chapters Four and Five.

Power Mac. But that's not all: New programs written specifically for the Power Macs run many times faster than on the highest-end Quadra.

Fortunately for Mac users, the speed offered by the Power Macs doesn't come at the price of incompatibility. Thanks to Apple's emulator, existing Mac software thinks it's running on a 68k processor.

These new Macs are based on a PowerPC chip, a product of the Apple/IBM/Motorola alliance formed in 1991. But the history of the RISC Mac started about three years earlier, when a group of Apple engineers began building a computer system.

#### **RISC** at Apple

Apple has been using RISC chips since the late 1980s and shipped its first RISC-based product, the Macintosh Display Card 8.24 GC, in March 1990. This graphics card used an AMD 29000 (29k) processor running at 30 MHz to accelerate graphics operations on the Macintosh. This acceleration was achieved by replacing code that would normally run on the Mac's own 68k processor with code that ran on the much faster 29000. Since only a specific part of the Macintosh operating system—the QuickDraw graphics software—was replaced by faster RISC code and not the entire operating system, the term toolbox acceleration was coined. Toolbox acceleration makes only the most computationally intensive parts of the Mac OS (operating system) run faster. Speeding up select parts of the operating system produces a performance increase perceivable throughout the system. The amount of engineering effort involved in converting only certain parts of the OS was also far smaller than the work required to make the whole thing native. Native software is developed specifically with RISC in mind and takes full advantage of the new processor's performance.

The 8•24 GC card was plagued with incompatibilities, even with Apple's own hardware and software, and it was ultimately abandoned. However, the 8•24 GC was a valuable proving ground for some of the technology found in the Power Macs. The idea of selectively converting the most performance-critical parts of the operating system carried forward to the Power Macs' system software. Power Macs use a hybrid of PowerPC code for QuickDraw, parts of QuickTime, and other compute-intensive parts of the OS, and emulated 68k code for those parts of the OS that wouldn't benefit as greatly from being run on the PowerPC chip.

Entire computer systems based on RISC date back to two distinctly separate RISC projects at Apple that started in the late 1980s.

#### Jaguar

The Jaguar project officially got under way in summer 1989, although it had been in various stages of planning since mid-1988. The goal of the Jaguar project was to create a microcomputer that had more raw compute-horsepower than any other personal computer on the market and that had a truly human interface that, for example, accepted spoken commands.

Jaguar was to take advantage of RISC's horsepower not only to perform more raw computation in less time, but also to redefine the features of a basic personal computer. To this end, the Jaguar group had its own hardware and software teams. The project was independent of any existing Macintosh projects, much the same way the original Macintosh project was separate from any Apple II–related projects.

Apple's fixation on differentiation from the Macintosh came from Jean-Louis Gassée, at the time the president of

#### Jaguar Spin-Offs

Parts of Jaguar have accompanied recent Macintosh releases, even though Jaguar itself never made it to fruition. The following designs originated in the Jaguar project:

- The industrial design introduced with the Centris 610 as well as the Quadra 800

- The Apple Adjustable Keyboard, which can be split down the middle to angle the two halves so that your hands are held at an ergonomically correct angle

The following were all released with the 68040-based Quadra 660AV and Quadra 840AV and were all results of development work for the original Jaguar system:

- Apple's AudioVision monitor, with its integrated high-quality stereo sound and built-in microphone tuned specifically for speech input

- The GeoPort high-speed telecommunications hardware and software modem technology

- PlainTalk speech recognition, also known internally at Apple as Casper

Apple Products. He insisted that the new machine be completely different from any other computer system. One of the original plans was to use Pink, the code name for a new operating system developed internally at Apple, as the standard operating system for this new machine. Pink ultimately became part of the Apple/IBM negotiations, and the project was spun off from Apple and turned into the joint venture Taligent, which is dedicated to developing and marketing the Pink operating system and related technology as stand-alone products.

Jaguar wasn't initially intended to be a high-volume mainstream system. Instead, mass-market RISC systems would follow sometime later. Shortly after Gassée left in early 1990, however, Apple refocused the endeavor to be a mainstream system: The new computer would be a Macintosh.

In late 1989, the Jaguar engineers started to search for a RISC processor. They visited virtually every RISC chip vendor to determine which chip would suit their needs best.

#### RLC

While work on the Jaguar was already under way, the early work on the machine that would evolve into the Power Macs began. The core engineering team that designed the Power Macs had previously designed the Macintosh IIfx. As the IIfx's development was nearing an end in late 1989, a pivotal get-together happened during a ski trip in Kirkwood, California. During this trip, the Cognac project was born.

The Cognac project was named obliquely after John Hennessy, a Stanford University professor who is a big RISC proponent and a cofounder of MIPS, the maker of the R4000 family of RISC microprocessors. When the IIfx was introduced in March 1990, the 8•24 GC card, Apple's first product built around toolbox acceleration, was introduced simultaneously. Cognac was an idea for a 68020- or 68030-

based Mac that also contained a 29k RISC chip to accelerate time-critical parts of the OS—more than just the QuickDraw acceleration found on the 8•24 GC.

Another part of the Cognac investigation resulted in a 68020 emulator running on a 29k in software. At the time, the emulator was in the proof-of-concept stages, to determine whether it was feasible to emulate a 68020 in software and whether the resulting emulator would provide good enough performance to be acceptable to users.

Ultimately, the Cognac investigation concluded that it wasn't a financially feasible product. There simply wasn't a way to produce a mass-market version of such a hybrid system with two main processors at a sufficiently low price.

In mid-1990, the 88100-based RLC project got under way. RLC was short for RISC LC, referring to the Macintosh LC, in whose flat box the new machine resided, and whose system software the new RISC-based system was to run.

RLC was designed to be inexpensive to implement, quick to market and exclusively RISC-based. Its goal from the beginning was to support the 68k via emulation. RLC was designed to be as compatible as possible with existing Mac hardware—no changes without good reason. Essentially, RLC took a Mac LC and replaced the 68020 processor with an 88100-based CPU and a 68020 emulator.

RLC and its 68020 emulator were up and running in January 1991. It was able to boot with unmodified 68k-based Mac LC ROMs and run System 7. Early versions of the Mixed Mode Manager—the system software that determines whether code is 68k or for the RISC processor and routes it appropriately—were also put into RLC to allow toolbox acceleration.

Mixed mode is a necessity for native and emulated software to work together seamlessly. The Mixed Mode Manager knows which code is 68k-based and needs to be run by the emulator, and which code is native RISC code that can execute directly on the built-in RISC microprocessor. When mixed mode was first conceived, little thought was given to native apps. These machines were expected to run 68k software in emulation, with an accelerated operating system. The emulator was assumed to run fast enough for this to be a realistic way of running 68k software. Another performance-critical part of the Macintosh OS, the Standard Apple Numerics Environment (SANE) was also converted to run on the 88100. SANE, available in the Mac since the beginning, enables applications to perform floating-point calculations even if no floating-point hardware is present. SANE running native on the 88100-based system drastically sped up floating-point performance for those apps that used it for floating-point calculations.

#### Searching Out RISC

Using a RISC chip for a personal-computer system that wasn't a workstation was considered daring at the time. Analysts vigorously decried RISC as a fad, since it hadn't caught on in the mainstream personal-computer market. It was evident to the Apple engineers, however, that RISC processors had a brighter future than their CISC counterparts, since RISC had much greater potential for performance improvement over time. The workstation market, with Sun Microsystems in the lead, had already discovered that RISC provided much higher computational performance than the more conventional CISC chip designs.

The Jaguar team eventually picked the Motorola 88110 RISC chip. That decision was not exclusively a result of the existing relationship between Apple and Motorola, but largely a technical one. The 88110 is a single-chip implementation of the 88000 RISC architecture that Motorola first showed the world in mid-1988. At the time, the only implementation of the 88000 (88k) architecture consisted of a three-chip set: an 88100 and two 88200s.

#### **Following Sun's Lead**

Sun migrated from 68k-based workstations when it introduced systems based on its own SPARC chip, soon to become the most widespread RISC chip in the workstation world. In some ways, Apple is now following that lead. Although Sun made the

transition to RISC with an installed base of far fewer 68k-based workstations than the existing number of 68k Macs, it was nonetheless a radical departure at the time. And history supports its decision—Sun's SPARCstations are successful products.

#### The Other Contenders

The Jaguar team's initial round of investigation into high-performance processor architectures was comprehensive. The team looked at MIPS' R4000, Sun Microsystems' SPARC, Digital's Alpha, AMD's 29000, Advanced RISC Machines' ARM (used in Newtons), AT&T's Hobbit, Hewlett-Packard's PA-RISC, and even Intel's N10, which was later named the i860. At the time, Apple disregarded IBM's POWER architecture, PowerPC's immediate ancestor, because IBM did not appear inclined to make it available to third parties.

The reasons why each of these architectures fell by the wayside were many and varied. Above all, Apple's executives wanted a partnership with a company that had a solid future and sufficient chip manufacturing capability, and whose chip architecture fulfilled Apple's needs for mainstream computer systems. This also meant that, ideally, Apple would get access to a whole processor family whose members could span the

range needed to make low-end, high-end, and portable systems rather than just a single class of computer.

Negotiations between Sun and Apple went quite far: Sun was to use the Macintosh interface as the standard user interface for its UNIX, and in return Apple would use chips based on Sun's SPARC architecture at the heart of its RISC systems. Despite strong proponents of this plan within Apple, the negotiations didn't succeed because Apple felt the manufacturing capabilities for SPARC were insufficient for its needs. At the time, Sun had not yet cut its deal with Texas Instruments to manufacture SPARC chips. Additionally, Apple engineers had reservations about some of SPARC's technical features and the limited breadth of the SPARC family.

The MIPS R4000 family was also a strong contender. In this scenario, the Macintosh user interface would be the alternate user interface for ACE, the

#### The Other Contenders (continued)

Advanced Computing Environment, Apple would then use the R4000 family of chips for its computer systems. ACE, the consortium that included MIPS, Compag, and Microsoft, intended to define a standard RISC-based hardware and software environ-tems vendors from using RISC instead of ment that would become the equivalent of the x86 standard in the DOS and Windows world. Despite the R4000's technical merits, because it's fiendishly difficult to write softhowever, Apple and MIPS didn't come to an agreement largely because Microsoft, Apple's primary competitor on the operating-systems side, was a driving force in the ACE alliance. In addition, MIPS' manufac-

turing volume was insufficient from Apple's perspective. The ACE consortium later collapsed primarily because of power struggles among its members but also because of Intel's successful lobbying to dissuade sys-Intel's x86 architecture.

Apple eliminated Intel's i860 mainly ware for. The i860 wasn't designed for the mainstream, and Intel wasn't willing to make the necessary modifications to turn it into a usable chip for an Apple computer. This inflexibility doomed further negotiations.

Motorola's 88000 family was interesting to Apple for several reasons. At the time, Compaq was also investigating RISC chips and its engineers liked the 88110. Both Motorola and Apple were trying to convince Compaq that the 88110 was a good choice. Motorola wanted more high-volume customers, and Apple didn't want to be the only one using the chip.

Apple made the 88110 decision in mid-1990 because Apple engineers considered the architecture sound, and Motorola's intentions for further development meshed well with Apple's plans.

The 88110 chip's feature set, in addition to being a singlechip implementation, was driven largely by Apple's requirements for a mass-market RISC chip. Apple's opinion carried a great deal of weight because Apple's purchasing volume would probably eclipse the combined sales volume of several other RISC chip vendors. Although the projected number of Power Macs sold is small compared to the projected sales figures for i486- and Pentium-based systems, it is huge compared to the sales generated by the primary RISC market until now: workstations.

After picking the 88000 architecture, the Apple engineers built prototype devices. One of the first was the so-called Cub card, an 88100-based NuBus card. The 88110 single-chip implementation of the 88k was not ready yet; the 88100/88200 multichip solution used on the Cub was close enough to the 88110 so that Apple's engineers could begin work on the emulator and other system-related projects. They also had software development tools that worked with the Cub card, so development could begin quickly. The first version of the 88k-based 68k emulator was developed on the Cub card. The Cub card soon led to the RLC.

#### RISC for the Mainstream

In early 1991, the Jaguar project was disbanded and folded into the existing Macintosh group. At this stage, Apple's RISC efforts were focused on the mainstream; they were not to be high-end, high-performance, high-price computers anymore. The 88110-based successor to Jaguar was built as a Macintosh and code-named Hurricane.

One of the pivotal points in the 88k-based Mac development came at a sales conference in mid-1991, where RLC was demonstrated to a large audience for the first time. Not only did it run with unmodified LC ROMs and LC system software, but one engineer successfully ran an Apple II emulator for the Macintosh, much to the amusement of all present: an emulator running on an emulator.

RLC's immediate successor was born on another ski trip, this time to Banff, Canada, in March 1991. This machine, housed in a IIsi case rather than the LC case, was the first RISC Mac based on the 88110 rather than the 88100/88200

combination, and it was used to continue work on the parts necessary to make the RISC Mac a viable product.

Even after Apple was well into 88110-based development, some people within Apple expressed market-related reservations about the long-term viability of the 88k family. Despite Ford Motor Company's commitment to using an 88k chip in its next-generation engine computer, no major computer manufacturer had chosen the 88k. The sales volume for the 88k family looked too weak, and Apple didn't want to be the only computer maker using the 88k. So Apple went looking for a RISC chip for the second time.

The first time around, Apple hadn't considered IBM's POWER architecture because it thought IBM was unwilling to let other companies use it. This misconception was cleared up during some of the early high-level talks between upper management at Apple and IBM that ultimately set the stage for the alliance. Even once it became an option, POWER still wasn't Apple's favorite, though: The only implementation of POWER at the time was a seven-chip set. Such a conglomeration was far too expensive and unwieldy for Apple's purposes, and it didn't look as if IBM would be able to design a more suitable version of a POWER processor within Apple's time frame.

While the upper corporate echelons at the two companies were talking about collaboration opportunities, the Apple and IBM engineers met for the first time. This meeting happened to be on a Friday, which was dress-down day at the Austin-based IBM Advanced Workstations and Systems Division, home of the POWER architecture; all the IBMers were in jeans. The Apple engineers, anticipating a meeting with a stereotypical bunch of Big Blue people, were all dressed up in suits. Needless to say, this was an unexpected situation for both sides.

A follow-up meeting, which included Motorola representatives, was held the next week. Apple invited Motorola because of the two companies' long relationship, a result of

#### **Clothing Cult**

While the talks were still between engineers and the actual agreements were still off in the future, the IBM contingent, having studied Apple's project-clothing cult, presented the second meeting's attendees with sweatshirts. The sweatshirts bore an IBM logo rendered in Apple's six corporate colors, whose I had an apple stem and whose M was

Motorola's logotype. Having blatantly violated all and sundry trademarks and thrown proper IBM decorum out the window, the head of the IBM delegation was anxiety-ridden about the possibility of the box containing the shirts bursting open on the luggage turntable upon their arrival at the San Jose airport.

Apple using chips from the 68k family in Macs. This relationship continued with the collaboration on PowerPC because Apple felt uneasy about committing the company's future to IBM, one of whose divisions was still a direct competitor to Apple's Macintosh business. Apple involved Motorola not only to have a second source for PowerPC chips, but also because Motorola is one of the few chip manufacturers in the world accustomed to producing quantities of chips in the millions.

#### **Deal of the Century**

Apple and IBM have traditionally been archenemies, so the world was surprised to hear about the Apple/IBM/Motorola alliance, whose memorandum of intent was publicly announced in July 1991 and whose details were announced later that year. The alliance consisted of five specific parts.

- Apple, IBM, and Motorola would collaboratively design and build a family of RISC chips, known as PowerPC, derived from IBM's POWER RISC architecture.

- The Apple/IBM joint venture Taligent would be formed to develop, market, and sell a new multiplatform objectoriented operating system that was already under development at Apple.

- Kaleida, another joint venture, would create crossplatform multimedia standards and authoring tools.

- PowerOpen, the specification for a hybrid UNIX system much like Apple's A/UX but that runs on PowerPC systems, would be codeveloped at IBM and at Apple—no specific company was created.

Based on IBM's AIX version of UNIX, the initial implementation of PowerOpen will provide the ability to run Macintosh software on UNIX-based PowerPC machines much like A/UX does today on 68k-based Macs.

Apple and IBM would cooperate to integrate Macs into IBM's enterprise networking systems.

Although neither Taligent nor Kaleida has shipped a product and a PowerOpen OS isn't available yet on Power Macintosh either, the PowerPC alliance has already produced its first results: The 601 chip was announced in September 1992, and the 603 chip was announced approximately a year later. The 604 was announced in early 1994, and the 620 should be announced before the end of the 1994.

IBM's POWER seven-chip set, known as RIOS—which is the Spanish word for "rivers" and doesn't have any particular code-name significance—was completely unsuitable for high-volume, low-cost products. These days, RIOS is often referred to as Power1 to distinguish it from Power2, a more recent multichip implementation of the POWER architecture. A project known as RSC, for RIOS single-chip, was already in development at IBM when the Apple/IBM/Motorola negotiations began. The RSC's design goal, however, was to create a straightforward implementation of RIOS without significant modifications.

When IBM's and Apple's engineers got together before the alliance was finalized to discuss how to implement POWER in a way that made sense for Apple, they soon realized that they could use POWER as a foundation, reworking its design and improving the architecture. IBM's willingness to turn POWER into PowerPC greatly contributed to the success of the alliance.

In their meetings, engineers from Apple and IBM recognized several shortcomings of the POWER architecture that prevented its low-cost, high-yield implementation for personal computers. Power1 was, after all, originally designed for workstations with less stringent cost constraints. The IBM engineers took the suggested design changes that resulted from these meetings and convinced IBM management that modifications to POWER were required. Management buy-in at IBM was necessary to override dissenting opinions and instances of "not invented here" syndrome in some divisions.

Similar problems were apparent on the Motorola side. Motorola's contribution to the alliance wasn't only in manufacturing and sales. Part of the PowerPC chips' hardware is based on designs that originated in Motorola's 88110 project. Although it was initially reluctant to share its technology, Motorola's technical contribution to the effort significantly enhanced the PowerPC's value to Apple by minimizing the reengineering of its 88k-based systems.

The successful evolution from POWER to the PowerPC architecture, which made high-speed yet inexpensive single-chip PowerPC implementations possible, is a testament to the willingness of the three companies to overcome significant hurdles in the interest of a mutually beneficial goal.

The first PowerPC chip, the 601, is an amalgam of RSC with enhancements, plus some features of the Motorola 88110. The PowerPC architecture was designed to be more suitable for typical personal-computer tasks, as well as to make evolution and expansion easier. The strengths of PowerPC's ancestors complemented the new architecture: POWER was originally designed for high-performance workstations, and the 88110 had a well-designed interface

between the chip and the rest of the computer system. The latter helped conserve the investment that Apple already had in its 88110-based designs. Only minimal hardware modifications had to be made to existing prototype systems at Apple to accommodate the differences between the 601 and the 88110.

#### Meetings, Phone Calls, Meetings

IBM entered negotiations with Apple because it was interested in having Apple adopt its RISC architecture; IBM also wanted access to the Pink operating system to run on its own hardware platforms. IBM's AIX group in Austin, however, wasn't particularly gung ho about putting the Mac user interface and application services on top of its UNIX. Hammering out the agreements between Apple, IBM, and Motorola took more than six months of frequent conference calls and face-to-face meetings held under the utmost secrecy and often in hastily furnished and otherwise unused IBM and Apple office space. Conference calls twice weekly between Apple and IBM kept everyone up-to-date. These calls were also intended to identify issues that could hinder the deal's completion.

Aside from those negotiating at the executive level, most IBM representatives at the meetings were from the Advanced Workstations and Systems Division, today known as the RS/6000 Division. No one from IBM's Personal Computer division, based in Boca Raton, Florida, was involved at any point. The PC division didn't originally commit to using PowerPC chips and even reserved the right to build MIPS-based systems in case the MIPS architecture turned out to be the RISC standard for Windows. IBM has since created a separate business unit as part of the Personal Systems Division that will build PowerPC-based, nonwork-station computers.

Several landmark meetings with Apple and IBM executives got the entire process under way. One such meeting made RSC+, the initial version of the 601, possible by IBM's agreement to change POWER into PowerPC. Another meeting paved the way for IBM's manufacturing specialists to agree on an aggressive delivery schedule for the 601's chipproduction process. The 601 went from design to production in less than two years—a considerable feat.

One of the first weeklong meetings was held in June 1991 in an otherwise abandoned building on IBM's Austin, Texas, campus. The day before this meeting began, IBM installed a network, computers, phones, copiers, furniture, and all the other necessary accourtements of a well-equipped meeting place. The meeting focused on PowerPC, Pink, and PowerOpen; Kaleida didn't enter the equation until later.

The same group of people reconvened one week later in the opulent Management Development Center training facility at IBM's corporate headquarters in Armonk, New York. Two further weeklong meetings were held here, focused on the same three issues. The final alliance agreement was made at meetings held in Apple's River Park facility in San Jose, California—office space that Apple had recently vacated but whose rent was still paid. Similarly to the first weeklong meeting in Austin, this venue was transformed from an abandoned space to a functional conference facility in a day. This final get-together, during which most everyone lived at River Park, resulted in the full set of Apple/IBM/Motorola agreements, including the birth of Kaleida, that formed what many people within the three companies call the deal of the century.

During the meeting at the River Park facility, each company had areas that were further subdivided by project: multimedia, PowerPC, Pink, PowerOpen, and Networking &

Communication. Because of the large number of attendees, everyone wore stickers, color-coded by company. Apple was red, IBM wore blue, and Motorola green. One of the Apple group's running jokes was that the meeting resembled *Star Trek*: Apple was the Federation; IBM was the Klingon empire with whom they were making peace; and Motorola was the Romulan empire—not because they were the badguys, but simply because they were the makers of the ROMs. Once again, pop culture and high technology collided.

#### Somerset

The PowerPC part of the Apple/IBM/Motorola alliance came together at Somerset, the PowerPC design facility opened in May 1992 in Austin, Texas. Initially dubbed the Customer Design Center, it was aptly renamed Somerset after the English legend of warring factions in the time of King Arthur laying down their arms and joining forces.

The first PowerPC chip, the 601, was designed primarily at an IBM facility in Austin, with the help of Apple and Motorola engineers, and completed at Somerset. The other members of the PowerPC family—the 603, the 604, and the 620—originated at Somerset. The Somerset facility is singular not just because of its joint-venture nature, but also because of its large staff and because it has the funding to allow the parallel development of multiple chips. The 603, 604, and 620 development went on simultaneously. (Many chip families are still designed in sequence, but even Intel is working on two generations of its x86 processor, the P6 and P7, simultaneously.) As a result of the parallel work at Somerset, all of the initially announced PowerPC chips should have reached first silicon by the end of 1994.

The 601 was produced in record time: a total of 21 months from concept to high-volume production. Development

started in October 1991, first silicon happened in September 1992, and volume production started in July 1993. As if this weren't challenge enough, the PowerPC architecture specification was being designed simultaneously with the 601 design, a process that took a total of six months, making life interesting for the chip designers by requiring changes in the chip's design at several steps during development because of changes in the architecture design. The complete PowerPC specification was finished well after work was under way on the 601. Considering that the members of the development team began as strangers, the successful completion of the 601 in that short period of time was no mean feat.

Of all the engineers at Somerset, the Apple contingent numbers fewer than 10. In addition to being vastly outnumbered, they all have dual roles to fulfill: They are chip-design engineers as well as customer representatives to Somerset. Since Apple will almost certainly be the largest single customer of PowerPC chips in the near term, Apple's needs carry significant weight in making design decisions.

The composition of all design teams at Somerset is strictly half IBM and half Motorola, except, of course, if an Apple engineer is part of a team. In the spirit of "trust but verify," this 1:1 ratio ensures that no one company's interest is better represented than that of another. Consequently, no features particularly beneficial to one of the companies make it in to a design. Since the distribution of the companies' employees has been a constant from the outset, much potential disagreement has been avoided outright. Many believe that this is a major factor in Somerset's success. Certainly, no one would have forecast that the 601 would be completed slightly ahead of schedule, especially since the outside world was waiting to hear stories about infighting between the factions.

## **Mixing Corporate Cultures**

Just because the majority of the Somerset engineers are from two companies not known for their casual corporate atmosphere doesn't mean that Somerset is a stuffy place to work. Overall, the Somerset environment is most similar to Apple's. When IBM was interviewing for positions at Somerset, dress-down day on Friday was touted as a perk. This notion is ludicrous to Apple people, and it was soon explained to the interviewers that they were more likely to scare away potential employees than lure them by offering casual Fridays.

Another example of culture clash is the question of drug testing: Apple doesn't, Motorola tests employees randomly with advance notice, and IBM makes testing compulsory. The policy adopted at Somerset was that employees are subject

to the personnel policies of their employers; no grand unified policy was set for Somerset as a whole. Another issue was alcohol. No alcoholic beverage is allowed in any IBM building; this is in stark contrast to Apple's traditional Friday-afternoon beer bashes in Cupertino. At Somerset, no alcohol is the norm, since both IBM and Motorola have similar policies.

Even if the predominant mode of operation at Somerset is casual, there are also extremes. In the early days, one member of the Apple contingent always arrived at meetings with a bag of rubber toys. At the start of every meeting, the bag's contents were dumped onto the meetingroom table, and anyone who needed to use a rubber fish to accentuate a point during the meeting could do so.

#### 601 Is Greater Than 88110

After all the political hubbub had died down and the engineers got to work, several things needed to happen. The most important task was to get the first PowerPC chip, the 601, specified, designed, and into production. While meetings between Apple, IBM, and Motorola people were going on, the Apple engineers who'd been working on 88110-based systems needed to shift into gear for PowerPC development. But since a real PowerPC chip was still quite a ways off, they initially used IBM's RSC processor, which was similar enough to allow productive work. The first system-on-acard similar to the Cub card was the RSC-based Smurf card,

named after a little blue thing (as opposed to a Big Blue one). Later versions of the Smurf card were 601-based. The 68k emulator was moved over to it, as were Apple's other RISC software projects.

Because of their active involvement with the 601 design, Apple's engineers were prepared when the first 601s appeared in September 1992. It took only a few days to get the 601 working on a Smurf card, and another two days until the emulator was running well enough to bring up the Finder. This impressive achievement was by far the fastest that Apple had managed to get Macintosh up and running on a new CPU. As one might imagine, it's rather more work to go from 68k to PowerPC than from 68020 to 68030 or from 68030 to 68040. Typically, getting a machine based on a new chip to boot all the way to the Finder takes weeks, rather than days.

After the deal of the century, many engineers both within Apple and within Motorola who had spent considerable time on 88110-based projects weren't too thrilled about switching over to the 601. Nonetheless, Apple's 88110 projects moved over to PowerPC. The Hurricane project switched over to the 601 and soon was renamed Tesseract, and RLC and its IIsi-boxed successor changed names to PDM, short for Piltdown Man. The engineers picked this name because of its symbolism: Piltdown Man was the supposed evolutionary missing link between the ape and *Homo sapiens*. In this analogy, the 68k world was the past, and the future was Jaguar's original spec, a non-Macintosh computer with a vast set of sophisticated but easy-to-use features. PDM, with a RISC core but still a Macintosh, was the missing link.

Since the PowerPC 601 has a virtually identical bus to the 88110, the hardware modifications needed to make the switch from RLC were minimal. The PDM's feature set was chosen deliberately to be less ambitious than that of Jaguar. The goal, as with RLC, was to minimize the risk involved in introducing RISC into the Macintosh world and to support 68k software via an emulator (by now in its third iteration), but with a high-end Mac feature set. At the time, the Cyclone project was under way, which would result in the Quadra 840av and Quadra 660av. PDM's design is deliberately similar to Cyclone's, since it was to offer a high-end, high-performance Macintosh feature set at an affordable price.

# **RISC System Software**

The development of RISC system software at Apple went through many iterations, much like the hardware. Work on many of the fundamentally new parts of System 7.1.2, the version of system software that shipped with the new Power Macs, began with the Cognac project, where the first 68k emulator running on a RISC chip was developed. The Mixed Mode Manager is another addition to the system, and it has also existed in various forms for several years. However, running System 7 on the Power Macs hasn't always been the clear choice, no matter how obvious it seems today.

Jaguar initially was slated to run Pink, Taligent's new object-oriented operating system, but the migration of the early RISC projects into the Macintosh realm changed the plan back to the Macintosh OS, albeit in a different form. Some within Apple wanted the RISC Macs to take on the workstation market as well, and as a result, they wanted a version of UNIX to be the standard operating system for the RISC Macs. For a month in early 1991, the upper echelons at Apple had to be convinced that the Mac OS, and not A/UX, should be the default operating system.

When the decision to go with PowerPC was made and PDM was in its early stages of development, an ambitious plan for system software was formulated. As attendees of the Apple Worldwide Developers' Conference in 1992 were to

learn, the planned evolution of the Mac OS was toward using a microkernel operating system. This new OS would provide features such as preemptive multitasking and hardware memory protection in addition to all the standard Macintosh operating-system services.

The amount of work required to make the Mac OS native and to integrate it with the microkernel was ambitious, to say the least. Although it made sense conceptually to have the next major Mac system-software transition happen simultaneously with the introduction of the new PowerPC-based Macs, the decision was made in July 1992 to scale back the initial RISC system-software effort. For this reason, the more conservative system-software specification, which included the emulator, the Mixed Mode Manager, the Code Fragment Manager, and substantial toolbox acceleration, was dubbed V0, since this version was a step before the original goal of a full microkernel OS. The decision to go with V0 had a major benefit: Since compatibility with existing Macintosh hardware and software is a primary goal for the Power Macs, keeping the changes to the operating system to a minimum greatly reduced the potential for incompatibilities.

When V0 was settled upon as the target, a large effort got under way to determine exactly which parts of the operating system should be made native, to maximize the effect of the PowerPC microprocessor. Many months of investigation and data-gathering resulted in a list of most frequently used parts of the operating system. The more often a particular part of the OS was used, the higher priority it received to be made native. In general, the 90/10 rule is in effect here: 10 percent of the code is used 90 percent of the time. So, to maximize the impact of the PowerPC for system software, finding that 10 or so percent was the key.

In the end, all of QuickDraw, the part of the Mac OS that produces graphics, was made native, as well as many other often-used and performance-critical parts of the OS. Because

of the Mixed Mode Manager's ability to switch back and forth between native PowerPC code and emulated code, emulated applications get the full advantage of the native parts of the OS.

## Diversification

A big milestone for the PDM project happened in October 1992, at the Apple Pacific sales meeting held in Hawaii. The PDM team was flown out to demonstrate the new PowerPC-based system to a large audience for the first time. The hardware and software for the demo were prepared at Apple, but armed with PowerBooks, the engineers zealously continued software development in Hawaii. Unfortunately, by continuing their work, they wound up breaking the system software.

Panic reigned until the hardware and software were on speaking terms and the demo was stable again—just in time, since it was the night before the demo. Unfortunately, the demo system was left on the stage overnight (the demo was to be a part of the next morning's talks) rather than being locked up and, when the members of the PDM team came to check the machine for the last time in the morning, it was dead. Completely. Perhaps a stagehand had bumped the PDM or inadvertently done something else to cause the machine's untimely demise.

Finally, after taking the system apart completely, reseating all the chips on the motherboard, and putting it back together, it worked again. No one understood why, but they weren't about to question it, since the demo was set to begin within 30 minutes. The machine was gingerly snuck onstage behind a curtain, and when the time came, the demo came off perfectly and the audience of Apple salespeople and executives was none the wiser.

This demo wowed the audience, among whom were Michael Spindler and Ian Diery. It reinforced to all present that the PowerPC-based Mac was a viable product.

#### Code Names for the 7100

In late 1993, Carl Sagan (the astronomer, not the Mac) became upset upon learning that his name was being used to refer to the midrange of the Power Mac line. He (and his lawyers) sent letters of complaint to Apple Computer as well as to the trade journal *MacWEEK*. From the letter, it was clear he believed Apple was planning to use his name as the product name. As a result of the brouhaha, the engineers changed the name to BHA. BHA is purported to stand for butt-head astronomer.

But it didn't stop there. As a result of Dr. Sagan's actions, the code-name change made it into the national print and radio news and became well publicized. In the first week of 1994, MTV called Apple to check out what was going on. It isn't clear whether it was just calling to check facts or whether it was claiming that "Butthead" was its intellectual property; regardless, the machine's code name was changed once and for all. The Power Macintosh 7100 was finally code-named LAW.

Soon after the demo at the sales conference, it became clear that a single RISC-based Mac wasn't going to be able to fill everyone's needs and that a broader product line was needed. In March 1993, the high-performance variant of PDM, code-named Cold Fusion and later known as the Power Macintosh 8100, was started. Three months later, the midrange machine controversially code-named Carl Sagan, and officially named the Power Macintosh 7100, was started as well, rounding out the product line.

In May 1993, the Apple Worldwide Developers' Conference contained a lot of PowerPC-related technical information and whetted developers' appetites for soon-to-be-available high performance at reasonable prices. However, Apple realized that not all developers would be able to have PowerPC-native products ready in time for the machines' release, so they had to rely on its 68k emulation capabilities. In a successful attempt to assuage developers' fears about the emulator's compatibility, Apple set up a room with prototype PowerPC machines and let developers test their software. The success rate was over 90 percent.

To top it all off, at MacHack in June 1993, the annual Macintosh technical conference and impromptu software-writing event, Apple engineers surreptitiously used a prototype PowerPC machine for people to demo their hacks on, without bothering to tell anyone. The assembled group wasn't told until it was all over that all these often nonstandard and otherwise borderline pieces of software ran on the emulator without a hitch. This was the audience to convince about the emulator's stability and compatibility. Running the hacks on a PDM proved the solidity of the emulator to even the most hardened cynics.

In July 1993, a separate PowerPC upgrade project was started with the intent of providing the most inexpensive PowerPC upgrade possible. The Power Macintosh Upgrade Card, code-named STP, took the minimalist approach and provided only the hardware absolutely necessary for an existing 68040-based Mac to become a Power Mac. The STP solution was also ideal for owners of the Quadra 700, 900, and 950, who would not have the opportunity to get a logic-board upgrade like owners of the Macs that share the same boxes with the three Power Macs.

Apple's PowerPC evangelism efforts began to bear fruit in 1993. Approximately two years before the introduction of the Power Macs, the PowerPC evangelists at Apple began canvassing developers to bring their software native as soon as possible. It was clear that key applications needed to be running native on the Power Mac on, or close to, the date of announcement.

Developers were divided into two camps, InsideTrack and FastTrack, to help them bring their apps native quicker. The small number of InsideTrack developers were those who had apps that Apple considered absolutely crucial to a successful launch of the new machines. The InsideTrack developers started work on their software the earliest and fought through numerous changes in the operating system and in

the development tools. The bleeding edge best described where they found themselves. Many of these developers used IBM RS/6000 workstations for development, since the Mac-based development tools weren't available early on. The larger group of FastTrack developers, those with key applications that ideally would be done when the Power Macs were introduced as well, got started later using the Mac-based development tools. Many of them managed to get their products ready in time for the Power Mac announcement, despite the later start.

Many milestones were reached during 1993. System software went alpha in June, and into beta in October. As the shipping date for the Power Macs drew nearer, logistical issues about announcement and availability of systems and upgrades became relevant. The original plan was to announce and ship PDM on January 24, 1994, the tenth anniversary of the Mac, and announce the later availability of the other two machines. This idea was soon nixed by Ian Diery, because he wanted to have not only a full product line available at launch, but sufficient inventory to be able to sell machines to people in volume. Some trade magazines reported this schedule change as a slip—far from it, since at the time the engineering schedules didn't change. The only difference was that there was more time to produce more inventory. The Power Macintosh announcement was also the only Macintosh roll-out where upgrades for previous Mac models were to be available the same day as the new systems. This was also a marked departure from previous announcements, where upgrades were available only many months after the systems' introductions.

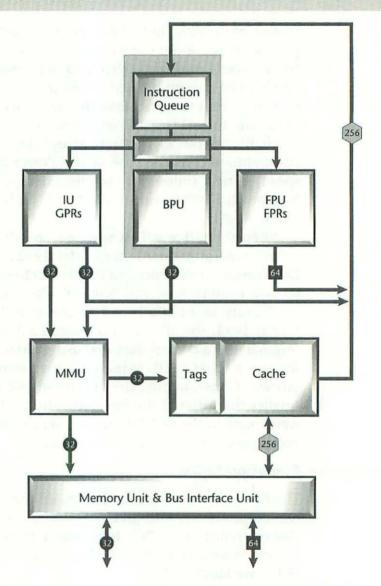

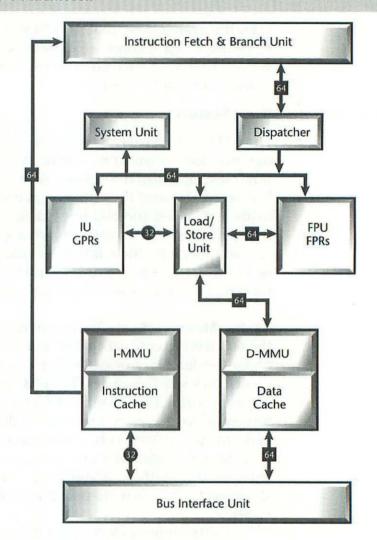

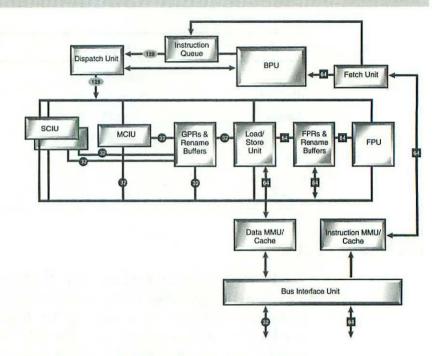

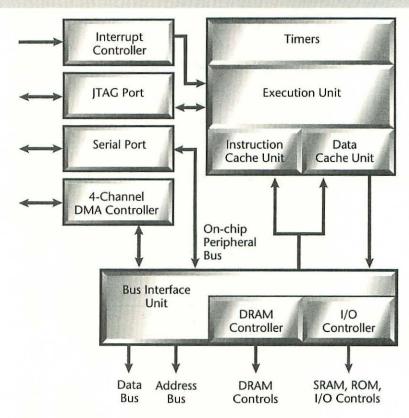

One of the final decisions to be made about the PowerPC-based Macs was their names. Speculation about their names ran rampant in the trade press and on online services. There was uncertainty whether they would even be called Macs. Within Apple, this question had an obvious