# 68000, 68010, 68020 Primer

### Stan Kelly-Bootle • Bob Fowler

MOTOROLA Series in Solid-State Electronics

# 68000, 68010 and 68020 Primer

Stan Kelly-Bootle and Bob Fowler

Howard W. Sams & Co., Inc. A Subsidiary of Macmillan, Inc. 4300 West 62nd Street, Indianapolis, Indiana 46268 U.S.A.

© 1985 by The Waite Group, Inc.

FIRST EDITION SECOND PRINTING-1987

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

The Waite Group has made every attempt to supply trademark information about company names, products, and services mentioned in this book. The trademarks indicated below were derived from various sources. The Waite Group cannot attest to the accuracy of this information.

8080, 8088/8086 and Intel are trademarks of Intel Corporation. AM-100 is a registered trademark of Alpha Microsystems, Inc. Apple is a trademark of Apple Computer, Inc. EXORciser, EXORmacs, EXORset, VERSAmodules, and VMEmodules are registered trademarks of Motorola, Inc. IBM and IBM PC are trademarks of International Business Machines, Inc. Lotus, 1-2-3, and Symphony are trademarks of Lotus Development Corporation. Macintosh is a trademark licensed to Apple Computer, Inc. MBASIC is a registered trademark of Microsoft Corporation. Radio Shack is a registered trademark of Radio Shack. WordStar is a registered trademark of MicroPro International Corporation. Z80 is a registered trademark of Zilog, Inc.

International Standard Book Number: 067-22405-4 Library of Congress Catalog Card Number: 85-61636

Typography by Walker Graphics Printed in the United States of America To my childers everywhere: Edmund Paul, Michèle Rose, Carol Ann, David Russell and rather late, alas, Anna Clare

-Stan Kelly-Bootle

To Guruprem Singh Khalsa, whose encouragement, inspiration, and vision over the years have helped to prepare me for this task

—*B*.*F*.

### **Acknowledgments**

We were tempted for a while to break with tradition, and claim that this book was entirely our own work, conceived, written and produced with no outside help whatsoever! Honesty and chivalry, though, combined with threats from certain quarters, finally convinced us that we should pay our respects in the customary manner.

First, we must thank Motorola's MOS Integrated Circuit Group without whom (as they say) our primer would undoubtedly be devoted to a less interesting and rewarding family of chips. In particular, we are grateful to James J. Farrell III, Technical Communications Manager, and Margaret Dickie at Motorola Inc., Austin, Texas for their courteous help with permissions, pictures and diagrams.

Our debt to writers on the M68000 and 16/32 bit micros in general is enormous and must here be condensed to a simple, nonexhaustive enumeration: Stritter, Treddenick, Scanlon, Starnes, Kane, Hawkins, Leventhal, Alexandridis, Waite, Morgan.

Editorially, we received encouragement from James Rounds of Howard W. Sams & Co., helpful advice from Dr. Roger C. Gledhill of International Micro Technologies, Inc., and much-needed cajolery from Mitch Waite and Jerry Volpe of The Waite Group.

On the production side, we would like to thank Lynella Cordell and her staff at The Waite Group, who together with Marla Rabinowitz and Walter Lynam resolved the many typographical and stylistic problems created by our keystrokes.

Our program examples were derived from work on the Alpha Microsystems Am-100/L<sup>™</sup> using their M68 Assembler. The authors wish to thank Alpha Microsystems and the San Francisco Chapter of AMUS (Alphamicro Users' Society) for their technical assistance. We also benefited from many informal discussions with Dr. Michael Godfrey of ICL, London and Bob Toxen of Stratus Computer, Inc., Boston. Nevertheless, we accept full responsibility for any residual bugs and welcome your polite corrections.

Stan Kelly-Bootle proclaims his everlasting devotion to his wife Iwonka and step-daughter Natasha Leof for their love and support throughout the project.

### **Contents**

1

40

55

Introduction viii

#### **1** Basic Microprocessor Concepts

**Microprocessors** 1 **Binary Arithmetic** 6 BCD — Binary Coded Decimal 10 Octal and Hexadecimal 13 Boolean Algebra 14 Microcomputers — the Three Components 20 Inside the MPU 25 Memories Are Made of This 29 Software — General Overview 36

#### 2 The M68000 Family

Introduction 40 The M68000 Success Story 44 Timing 46 Why 16-Bit? 49

#### 3 M68000 Programmer's Models

Levels of Programming 55 M68000 Instruction Set — Brief Introduction 61 Memory Model 62 Register Model 68 M68000 Basic Register Model 71

V

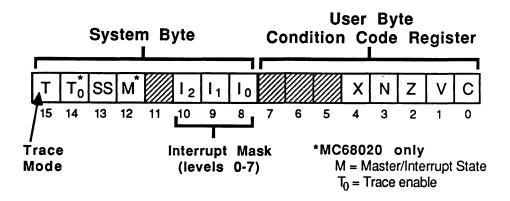

Register Arithmetic79Address Registers83System Byte84

#### 4 M68000 Instruction Set — First Steps

91

Instructions91Addressing Modes106Absolute Addressing Modes116Address Register Indirect Memory Addressing Mode124Address Register Indirect with Post-Increment: (An) +128Address Register Indirect with Pre-Decrement: -(An)133

#### 5 M68000 Instruction Set — Advanced Topics 135

Preserving Register Values — Why and How 135 Stacks 138 Address Register Indirect with Offset 147 Address Register Indirect with Offset and Index 149 Index Mode — Applications 150 Multiplication 151 Division 153 Relative Modes --- Motivation 158 Relative Addressing --- Program Counter Addressing with Offset 159 Relative Addressing — Program Counter with Offset and Index 163 Addressing Modes — Grand Summary 165

#### 6 Miscellaneous M68000 Instructions

**Bit Manipulation** 172 Logical Operations 173 Shift and Rotate Instructions 187 200 Rotates Bit Testing and Setting 204 Compare with the CMP Family of Instructions 214 222 Miscellaneous Math Multi-Precision Math 225 **Binary Coded Decimal** 229 Miscellaneous Data Handling 233 Link/Unlk — Preamble 237

172

| 7           | The MC68010                                                                                                                                                                                                                              | 252               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|             | Virtual Memory 253<br>Virtual Machine 256<br>Vector Base Register 258<br>The MOVEC and MOVES Instructions 261<br>The SFC and DFC Registers and Address Spaces 262<br>Loop Mode 264<br>The MC68012 265                                    |                   |

| 8           | The MC68020                                                                                                                                                                                                                              | 266               |

|             | Instruction Cache 266<br>New Addressing Modes 274<br>Trace Bits T0 and T1 278<br>Coprocessor Support 280<br>The Master Bit 285<br>New Instructions on the MC68020 288                                                                    |                   |

|             |                                                                                                                                                                                                                                          |                   |

| A           | M68000 Instructions — Number of Operands                                                                                                                                                                                                 | 295               |

| A<br>B      | M68000 Instructions — Number of Operands<br>M68000 Addressing Mode Types                                                                                                                                                                 | 295<br>297        |

| B           |                                                                                                                                                                                                                                          |                   |

| B<br>C      | M68000 Addressing Mode Types                                                                                                                                                                                                             | 297               |

| B<br>C      | M68000 Addressing Mode Types<br>M68000 Instructions/Legal Modes                                                                                                                                                                          | 297<br>300        |

| B<br>C      | M68000 Addressing Mode Types<br>M68000 Instructions/Legal Modes<br>M68000 Instruction Summary<br>68000 Addressing Modes 303<br>Addressing Mode Orthogonality and Legality 307                                                            | 297<br>300        |

| B<br>C<br>D | M68000 Addressing Mode Types<br>M68000 Instructions/Legal Modes<br>M68000 Instruction Summary<br>68000 Addressing Modes 303<br>Addressing Mode Orthogonality and Legality 307<br>The 68000 Instruction Summary Table — Preliminaries 310 | 297<br>300<br>303 |

### Introduction

This primer is intended for the growing number of programmers and hobbyists, both novice and experienced, who want to understand the powerful **instruction set** of the Motorola M68000 family of 16/32-bit microprocessors. The instruction set represents the language built into the chip, and ultimately, all programs written for the M68000, whether in ADA, BASIC, C language, assembly language, or whatever, need to be translated "down" to this level.

With 8-bit micros it was tricky but possible to hand code at the machine level without assemblers. With 16-bit instruction words (up to seven of them per instruction) hand coding is strictly for masochists too tight to buy an assembler. So the M68000 instruction set will usually be studied in the context of an assembler.

The authors' attempts to master M68000 assemblers revealed a monstrous, horrifying gap in the literature. There was no patient elementary introduction even to those basic instructions and addressing modes that are common to all M68000 models. More understandably, there were no popular expositions of the exciting extensions available on the MC68010 virtual machine chip and the full-32-bit mainframe-micro MC68020. This primer is our selfless attempt to fill both gaps.

You can view the book as a painless "first pass" for all those who wish to gain fluency in any of the many fine M68000 assemblers and cross-assemblers now available (see Appendix E).

Assembly language documentation can be pretty daunting unless you already understand how the op codes work, and many of the manuals are less than clear on which addressing modes are legal with which instruction. Beyond that you face the hurdles of directives, macros, conditionals, libraries, linkers, overlays, monitor calls, and so on — all of which can vary from assembler to assembler.

Yet the rewards are great. Quite apart from the obvious advantages — speed and compactness (notice how often advertisements for software boast,

"Written in tight, fast assembly language!"), we know of no greater joy in computing than successfully running one's own first sizeable chunk of assembled code. There is a feeling of, "Wow, we did it – the 68000 and me!"

Our book should also be useful for those wanting to experiment with the various M68000 educational single board kits and systems.

We have purposely avoided a detailed exploration of the M68000 microelectronics and IC technology. Our bird's eye view of the M68000 hardware is a simple "black-box" approach, but sufficient, we hope, to reveal the subtle interplay of hardware and software as realized by the Motorola design team. If you want to delve deeper (and in the field of computers there is no bottom layer beyond possible delving) this book will help you tackle the vast technical literature on M68000 architecture and timing, support chips, I/O, coprocessors and systems integration.

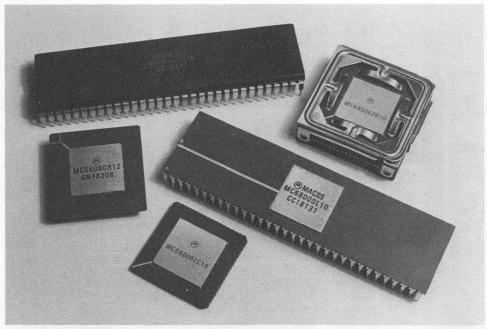

Success breeds success — a maxim which is compounded in the microcomputer industry. All semiconductor prices fall dramatically as fabrication volume and yield increase, so successful chips like the M68000, especially the economy MC68008 version, are inevitably finding their way into the low-cost entry-level personal and home computer market. The basic MC68000, now available for around \$50 each in small quantities, can already be found playing diverse roles in graphics workstations and multiuser business systems — not only on the main CPU (central processing unit) board, but also powering intelligent device drivers and I/O (input/output) preprocessors. Even the more expensive MC68010 is found lurking inside peripherals, such as the Apple laser printer.

The MC68020 chip, currently selling for \$500 in small quantities, seems certain to fall in price to the MC68000 level over the next few years. The impact on personal and office computing will be staggering!

The Apple Macintosh has already given us a glimpse of what can be done with the power of a basic 16/32-bit MC68000. The user-friendliness we associate with crisp, bit-mapped screens, icons, windows, and mouse-controlled pulldown menus puts heavy demands on CPU and memory.

The MC68020's extra speed (16.67 MHz, with fast RAM to match), lower power consumption (1.5 watts), built-in coprocessor interface for economical multiprocessing and number-crunching support, and increased memory addressing space (over 4 billion bytes) — will allow bigger and friendlier operating systems, more complex color graphics (including animation), and less unnatural high-level query languages providing easier access to large databases.

An added bonus will be the ability to offer several operating systems on the same machine, solving many of the present compatibility quirks ('what runs on what?'') and ending once and for all those tiresome medieval disputes such as "UNIX versus AMOS" or "CP/M versus PC-DOS." Our book will prepare you for this revolution! All members of the M68000 family share the same basic instruction set, with each enhanced model building up from the previous simpler model. This concept of **upwards compatibility** at the object code level provides vital insurance for all software developers, both the individual "hacker" and the major software houses. For as fast as hardware prices shrink, the cost of programming escalates. The M68000 was designed with ease of programming and debugging in mind, and further, with the assurance that whatever advances might occur in IC techniques, programs will run without change on all future models. We will all undoubtedly have new things to learn as the revolution unrolls apace, but readers should be happy to know that little in this book will have to be *unlearned*.

#### PREREQUISITES

Exactly how much prior knowledge should be assumed is a problem faced by all computer book authors. We have veered in the direction of assuming less rather than more exposure to computer basics, and we rely on your own judgment to skip any familiar material.

Chapter 1, for example, is a quick summary of some essential microprocessor concepts that you are invited to bypass at your own discretion.

Our strategy was conditioned by the fact that a new generation of programmers, the class of '85, is entering the field with little or no prior exposure to the previous (dying?) generation of 8-bit micros. If you have done any assembly language programming on the Intel<sup>TM</sup> 8080<sup>TM</sup>, Zilog Z80<sup>TM</sup> or Motorola M6800, for instance, many of the M68000 op codes will be old friends (at least functionally), and you will be able to concentrate on the subtleties introduced by the richer set of addressing modes. But for those new to the world of op codes, we have tried to explain both the function and the motivation for each instruction, with lots of simple examples. We have carefully chosen the order in which the instructions are introduced, grouping together those which share some fundamental property.

There are four appendices (A - D) that list the op codes and addressing modes in different ways, plus a pullout reference card.

#### **BOOK PLAN**

After the optional basic concepts in Chapter 1 (we dismissed the corny notion of calling this Chapter 0), Chapter 2 gives some historical and design perspectives and lists the features distinguishing the five M68000 models currently available. Chapter 3 explains the chip from a software perspective (memory organization and register disposition). The instructions and addressing modes

are then progressively described with examples, starting with the most common and useful in Chapter 4, accelerating gently to more advanced op codes in Chapter 5. Chapter 6 deals with the remaining instructions. Chapter 7 explains the VM concept in relation to the MC68010. Finally, Chapter 8 discusses the many enhancements found in the new full-32-bit MC68020.

#### M68000 RESOURCES

If, as we hope, you are encouraged to explore the M68000 scene in more depth, we have listed some sources for hardware and software in Appendix E. Be warned that no such list can claim to be complete or entirely accurate by the time you come to read it. Prices and telephone numbers are especially volatile.

As you can see, the M68000 has been implemented in an incredibly wide variety of microcomputer systems, ranging from the under-\$500 home computers, through the sophisticated \$1,500-\$3,000 personal computer bracket (highlighted by the ubiquitous Apple® Macintosh<sup>™</sup>), on through the professional \$5,000 + UNIX<sup>™</sup> workstations (from over 20 different manufacturers at our last count) — the IBM® 9000 laboratory system, multiuser business systems from AlphaMicro, Stride, Cromemco — the list grows daily.

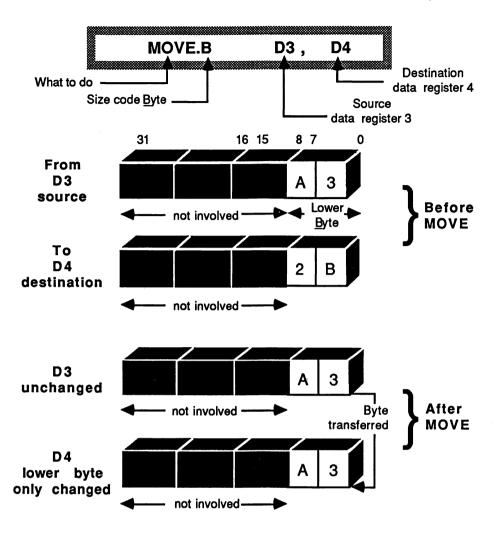

From \$200 to \$200,000, they all use **MOVE.z Dm,Dn**! When you reach Chapter 4, you'll know why.

# 1

## Basic Microprocessor Concepts

Inasmuch as the completed device will be a general-purpose computing machine it should contain certain main organs relating to arithmetic, memory storage, control, and connection with the human operator.

A. W. Burkes, H. H. Goldstine, and J. von Neumann, Preliminary Discussion of the Logical Design of an Electronic Computing Instrument (1946)

This chapter presents a number of useful basic ideas that you will need to better understand the M68000 family. Primers, by definition, cannot assume too much prior knowledge, so we will warn you, up front, that we plan to cover such fundamentals as bits, bytes, binary arithmetic, and busses which are essential for later chapters.

#### MICROPROCESSORS

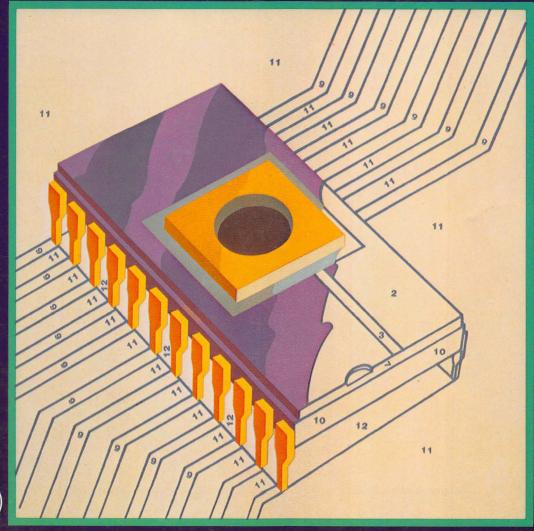

On first hearing the word *microprocessor* one immediately senses that we are talking of something small, and it is indeed a physically small computing component on a silicon chip (*micro* is a common prefix in science standing for a millionth part, as in microsecond).

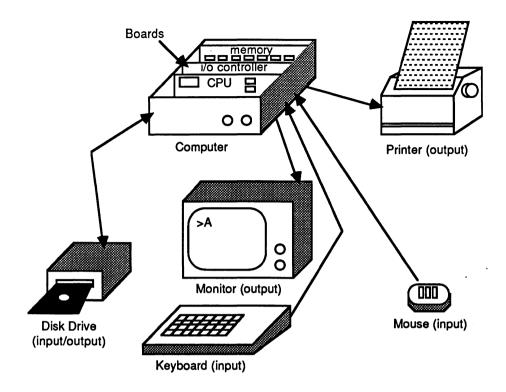

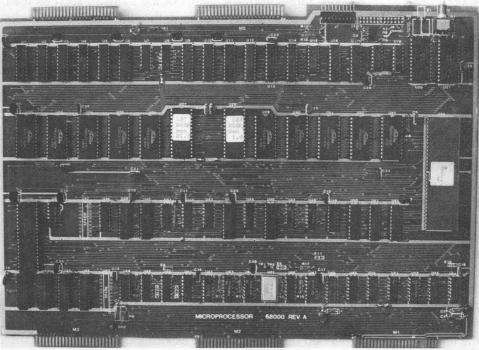

The MPU (MicroProcessing Unit) is just one element, or resource, in a computer **system**. Figures 1-1 and 1-2 show typical computer systems. The MPU chip, when mounted on a circuit board with other essential supporting chips, is often referred to as a microcomputer or an MPS (MicroProcessing System) or a CPU (Central Processing Unit).

Fig. 1-1 Typical Small Computer System

The MPU is often called the brains of the system, the resource with programmable intelligence that coordinates all the other dumb elements connected to it. MPUs have logical and arithmetical abilities, and they make decisions and exert control in many ways. You will see, however, that all this occurs in a predetermined way, set up by **programs** (sequences of precise instructions).

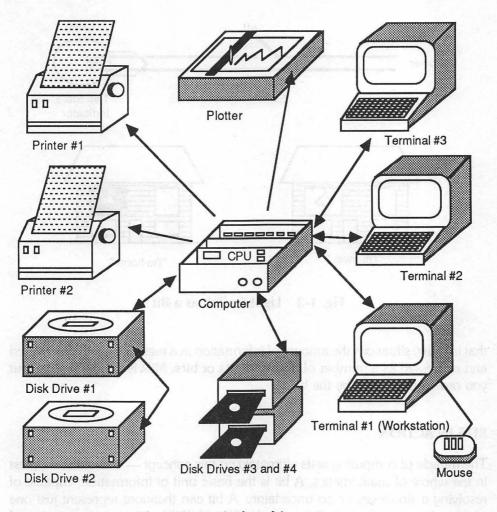

MPUs are no longer the most expensive component in the system, and several MPUs may be found in the one system (which is then labeled a multiprocessor system). Quite often there is one **master** MPU with several **slave** MPUs assigned to particular duties; sometimes each MPU is an independent source of intelligence that can be called on to process any job.

#### **PROCESSING WHAT?**

But what and why are you processing? Cuisinarts process food, and sewage plants process sewage, but microprocessors process **data** and (with the help of many attached gadgets and carefully detailed programs) they produce **information**.

Fig. 1-2 Typical Multiuser System

If this sounds abstract and intangible, well, in a sense, it is. The computer is a very general-purpose, blind manipulator of symbols — it is you, the user, who gives meaning and purpose to its processes.

Throughout the following discussions, we will use the word data as a singular, collective noun.

#### Information and Data

Information, in everyday usage, is a strange something that reduces uncertainty. In the 1940s Claude E. Shannon of Bell Labs refined this vague idea into a whole new branch of mathematics, known as **information theory**. He showed

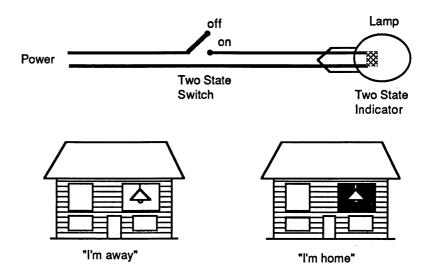

Fig. 1-3 Light Switch as a Bit

that in many situations the amount of information in a message can be measured and expressed as a number of **binary digits** or **bits**. Milk is traded in pints, but you order information by the bit.

#### **BITS IN ACTION**

The miracle of computing rests ultimately on this concept — one of the simplest in the whole of mathematics. A bit is the basic unit of information, capable of resolving a single yes or no uncertainty. A bit can therefore represent just one of two values, usually given the symbols "0" and "1", but that can be interpreted in many ways: on and off, black and white, true and false, yes and no, but note that the bit is incapable of indicating any shades in between, like gray or maybe or perhaps.

It turns out that many physical devices, such as the familiar household electric switch, have this same on-or-off property and can therefore be used to store one bit of information.

Devices like switches which have a limited number of states are called **discrete** devices, as opposed to devices like rotary volume controls which can vary continuously through an infinite number of states.

In Figure 1-3, the state of the switch is indicated by the state of the lamp, on or off.

The information you could signal from your window using this simple onebit device might be "Yes, I am here" or "No, I'm out of town." Ah-ha, but which is which? "Lamp-on" could signal your absence, perhaps. The message of the lamp requires a prearranged code between you and the intended receiver of the message. There are only two possibilities:

| Code A            | Code B             |

|-------------------|--------------------|

| Lamp on = at home | Lamp on = away     |

| Lamp off = away   | Lamp off = at home |

The main point is that the bit as a bearer of information is meaningless without some prior coding agreement between sender (encoder) and receiver (decoder).

Shannon defined the bit as the amount of information that would make something twice as definite! Two equally likely outcomes share a probability of 1/2 (a 50/50 chance of each), so one bit will completely resolve this amount of uncertainty, but no more. For more useful information storage you need to increase the number of bits, and at the same time devise methods for rapidly storing, accessing, changing, sending, and decoding the information.

Each bit you add to your store doubles the amount of information. For example, with two lamps in your window, you can devise a code to represent four distinct messages:

| Lamp 2 | Lamp 1 | Message             |

|--------|--------|---------------------|

| off    | off    | Leave no milk today |

| off    | on     | Leave one pint      |

| on     | off    | Leave two pints     |

| on     | on     | Leave three pints   |

Once again you must ensure that the decoder (milkperson, in this case) knows the code, and especially, which lamp is which. If the lamps are not marked or distinguishable in some way, you can see that only three possible messages can be encoded. So, in order to extract the maximum benefit from our 2 bits, they must be ordered in a prearranged manner. With this proviso, there is a simple rule relating the number of bits to the number of possible encoded messages:

| 1 bit  | can encode 2                                   | (21) messages              |

|--------|------------------------------------------------|----------------------------|

| 2 bits | can encode $2 \times 2 = 4$                    | (2 <sup>2</sup> ) messages |

| 3 bits | can encode $2 \times 2 \times 2 = 8$           | (2 <sup>3</sup> ) messages |

| N bits | can encode $2 \times 2 \times \ldots \times 2$ | (2 <sup>n</sup> ) messages |

For this reason, powers of 2 play a fundamental role in information theory and computing.

The case of N = 10 is also important, since  $2^{10} = 1,024$ , which is widely abbreviated to K (as in kilo). So when you read of a 32K memory, this means  $32 \times 1,024 = 32,768$  rather than 32,000.

The messages you encode can be anything you like — instructions, symbols, numbers, names, or perhaps even nothing at all (a perfectly valid message might be "ignore this message"). Some combinations of bits may be specially earmarked as errors. Often there are more bit patterns available than messages to be decoded. This redundancy can be exploited to detect and possibly correct transmission or storage errors.

#### **BINARY ARITHMETIC**

There is a natural way of relating these bits to familiar decimal numbers — we call it **binary arithmetic** because it uses powers of 2 with the two symbols 0 and 1, rather than powers of 10 with the ten symbols 0 through 9. Nearly all computer calculations are performed internally in binary arithmetic, even if the final results are needed in decimal form. Our two-lamp code for ordering milk has already given a hint of how this works. Given the following code:

Lamp on

$$= 1$$

Lamp off  $= 0$

Lamp  $2 = 2$  Lamp  $1 = 1$

these would be the results:

| Lamp 2 | Lamp 1 | of pints |

|--------|--------|----------|

| 0      | 0      | 0        |

| 0      | 1      | 1        |

| 1      | 0      | 2        |

| 1      | 1      | 3        |

The decoding rule is:

pints =  $(2 \times \text{Lamp } 2) + (1 \times \text{Lamp } 1)$

| Lamp 3 | Lamp 2 | Lamp 1 | of pints |

|--------|--------|--------|----------|

| 0      | 0      | 0      | 0        |

| 0      | 0      | 1      | 1        |

| 0      | 1      | 0      | 2        |

| 0      | 1      | 1      | 3        |

| 1      | 0      | 0      | 4        |

| 1      | 0      | 1      | 5        |

| 1      | 1      | 0      | 6        |

| 1      | 1      | 1      | 7        |

With three lamps we can extend our order to 7 pints as follows:

Lamp 3 now carries the value  $4 = (2 \times 2)$  and we decode as follows:

pints = (4 x lamp 3) + (2 x lamp 2) + (1 x lamp 1)

You can already recognize the similarities between our usual decimal notation and this binary system. Treating the lamps as column positions, each column represents a power of 2. When you write, say, 2379 in decimal, you are using a shorthand for

2 thousands 3 hundreds 7 tens 9 units  $2 \times (10 \times 10 \times 10)$  plus  $3 \times (10 \times 10)$  plus  $7 \times 10$  plus  $9 \times 1 = 2379$

where each column represents a power of 10. The units column may not look like a power of 10, but in fact it represents 10° which equals 1.

In the same way, the binary number 1101, is evaluated as:

1 eight 1 four 0 twos 1 unit  $1 \times (2 \times 2 \times 2)$  plus  $1 \times (2 \times 2)$  plus  $0 \times 2$  plus  $1 \times 1 = 13$

We can therefore establish a straightforward correspondence between bit patterns, binary numbers, and decimal numbers. This is just one of many encoding schemes and must be agreed upon in advance as in any scheme for sending information.

To stress the role of the bit let's look again at our 3-lamp signals to the milkperson. Initially, the number of pints needed is uncertain to the extent that it lies anywhere in the range 0 through 7 (8 possibilities). Lamp 1 reduces this uncertainty as follows:

Lamp 1 on = number of pints must be 1, 3, 5 or 7 Lamp 1 off = number of pints must be 0, 2, 4 or 6 The uncertainty is now down to four possibilies, so it has effectively been halved. Lamp 2 and Lamp 3 each independently halve the uncertainty:

> Lamp 2 on = number of pints must be 2, 3, 6 or 7 Lamp 2 off = number of pints must be 0, 1, 4 or 5 Lamp 3 on = number of pints must be 4, 5, 6 or 7 Lamp 3 off = number of pints must be 0, 1, 2 or 3

All three bits (lamps) in parallel completely remove the uncertainty — just one of the eight possible messages is indicated.

The modern computer uses exactly these principles in sending and decoding messages and data. The switches and lamps are replaced by large numbers of high-speed two-state electronic devices such as transistors built into silicon chips.

#### SUMMARY OF BITS AND MESSAGES

With an ordered group of N bits you can encode up to  $2^{N}$  distinct messages. A common encoding system relates these to the  $2^{N}$  binary numbers running from 0 through  $2^{N} - 1$ . Since binary numbers can be easily stored electronically in the form of on-off switches (or gates), computers perform all their basic arithmetical and logical operations in binary.

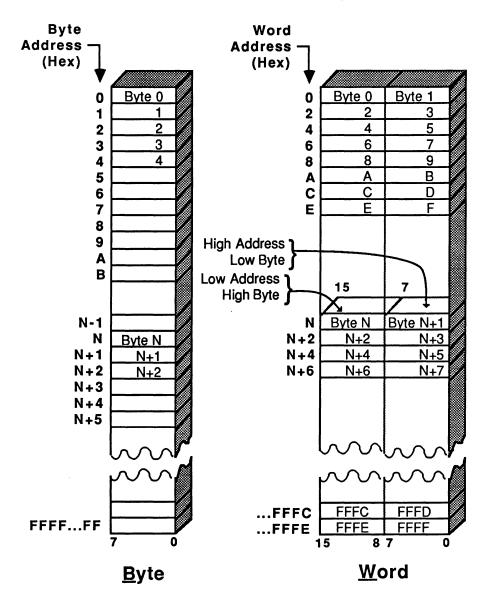

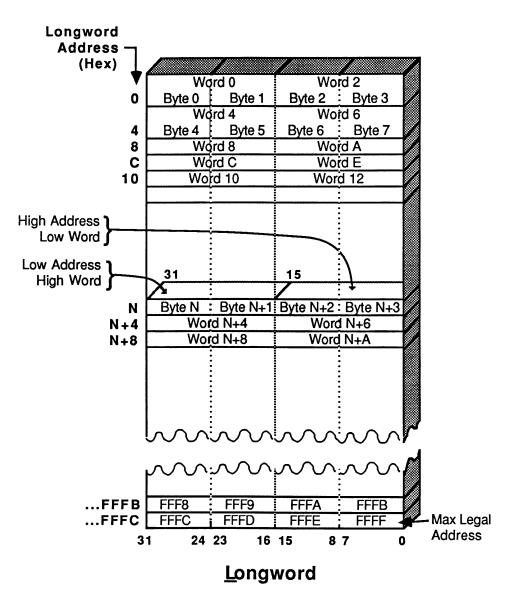

#### **Special Groups of Bits**

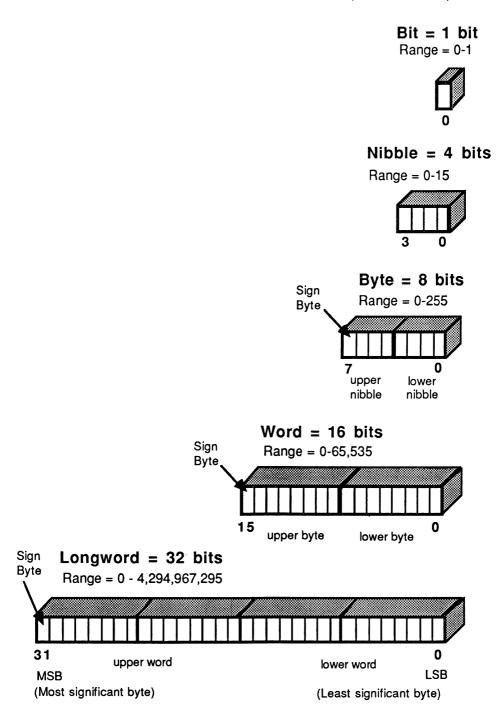

Groups of 4, 8, 16, and 32 bits are so commonly encountered that they have their own names:

- A nibble = 4 bits, which can store 16 messages

- A byte = 8 bits, which can store 256 messages

- A word = 16 bits, which can store 65,536 messages

- A longword = 32 bits, which can store 4,294,967,296 messages!

These names and their associated "ranges", will crop up repeatedly because, for excellent reasons to be explained, the M68000 is designed to operate on these groups of bits.

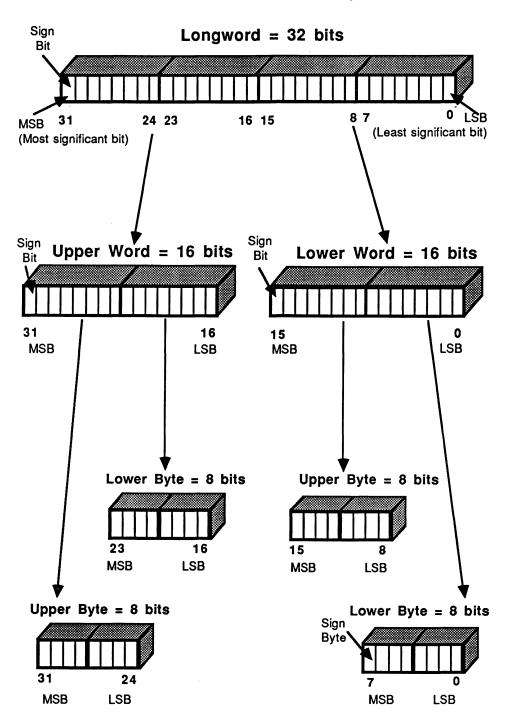

Notice in Figure 1-4 how the bits are numbered from right to left, starting with bit 0, called the LSB (least significant bit). The highest, leftmost bit is called the MSB (most significant bit); because of a commonly used method of encoding negative numbers, the MSB is also called the **sign bit** (more on this later).

Fig. 1-4 Groups of Bits: Nibble, Byte, Word, Longword

#### **BCD** — **BINARY CODED DECIMAL**

One important use of the 4-bit nibble is to encode the 10 decimal digits 0 through 9. Three bits will only encode 0 through 7, so four bits is the minimum. The resulting code, known as BCD (binary coded decimal), has five unassigned combinations. They, and the binary codes for decimals 0 through eleven, are shown here:

| BCD          | Decimal |

|--------------|---------|

| 0000         | 0       |

| 0001         | 1       |

| 0010         | 2       |

| 0011         | 3       |

| 0100         | 4       |

| 0101         | 5       |

| 0110         | 6       |

| 0111         | 7       |

| 1000         | 8       |

| 1001         | 9       |

| 1010         | unused  |

| 1011         | unused  |

| 1100         | unused  |

| 1101         | unused  |

| 1110         | unused  |

| 1111         | unused  |

| (0001)(0000) | 10      |

| (0001)(0001) | 11      |

This coding scheme is rather inefficient, space-wise. Compare, for example, the two ways of expressing the decimal 2379:

2379 decimal = 100101001011 binary (12 bits)2379 decimal = (0010)(0011)(0111)(1001) BCD (16 bits)

The main application of BCD is in financial calculations where some of the accuracy problems you can get with binary-decimal conversion are unacceptable.

#### **ASCII CHARACTER CODE**

The byte's claim to fame is that 256 is a useful number for encoding a set of characters, such as those on a typewriter keyboard. The upper- and lower-case

| Binary | 1's Complement<br>Mode | 2's Complement<br>Mode | Unsigned<br>Mode |

|--------|------------------------|------------------------|------------------|

| 0111   | 7                      | 7                      | 7                |

| 0110   | 6                      | 6                      | 6                |

| 0101   | 5                      | 5                      | 5                |

| 0100   | 4                      | 4                      | 4                |

| 0011   | 3                      | 3                      | 3                |

| 0010   | 2                      | 2                      | 2                |

| 0001   | 1                      | 1                      | 1                |

| 0000   | 0                      | 0                      | 0                |

| 1111   | -0                     | -1                     | 15               |

| 1110   | -1                     | -2                     | 14               |

| 1101   | -2                     | -3                     | 13               |

| 1100   | -3                     | -4                     | 12               |

| 1011   | -4                     | - 5                    | 11               |

| 1010   | - 5                    | -6                     | 10               |

| 1001   | -6                     | -7                     | 9                |

| 1000   | -7                     | -8                     | 8                |

Table 1-1

Decimal Interpretation of 4-Bit Binary

letters plus the usual crop of punctuation symbols and controls (carriage return, backspace, etc.) take up only 128 combinations (encodable in 7 bits) but since the 8-bit byte offers 256, we have lots of spares for graphics. There is a standard called ASCII (American Standard Code for Information Interchange) which assigns a symbol for each 8-bit pattern. Apart from a few variants for foreign scripts, ASCII is pretty constant around the world.

#### HOME ON THE RANGE

The byte can only store numbers in the unsigned range 0 through 255, so for most mathematical operations we need more than 8 bits. The situation is even worse because in order to handle negative numbers, we must steal a bit to indicate the sign (0 for plus and 1 for minus).

Under what is known as 2's complement notation (see Table 1-1) a nibble can store a number in the range -8 through +7 (still a total of 16 distinct numbers) and a byte can store a number in the range -128 through +127 (note that we are still encoding a total of 256 distinct numbers).

The bits in a byte are numbered 0 through 7 from right to left (so remember the first bit on the right is bit 0). In 2's complement form bit 7 (the leftmost) is designated the **sign-bit**.

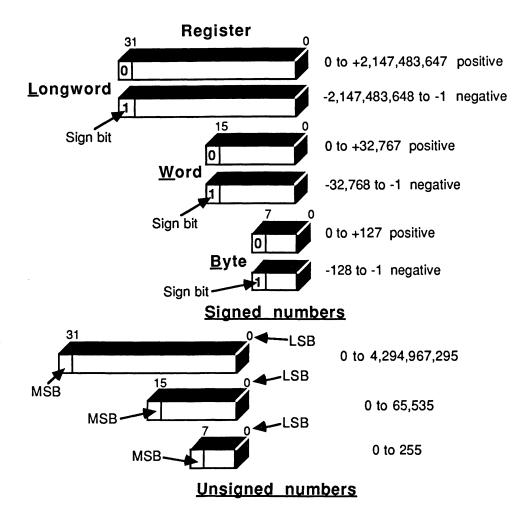

The 16-bit **word** offers a range of 0 through 65,535 unsigned (that is, positive numbers), but if we use the sign-bit trick for negative values we can store signed (2's complement) numbers from -32,768 to +32,767.

Before the arrival of 32-bit micros, the above 16-bit data range was a restriction needing extra programming if your sums led to larger numbers. Also since 16 bits were often used to encode addresses in memory (more on this later) this resulted in a more tricky restriction on memory capacity to 65,536 different addresses (again, there were tricks in hardware and software to overcome this).

You can now guess why there is so much excitement over the arrival of 32bit microprocessors. A 32-bit **longword** can store unsigned numbers in the range 0 through 4,294,967,295, and signed numbers in the range -2,147,483,648 through +2,147,483,647. And when you are not doing big sums, the longword can store two smaller 16-bit numbers, or four ASCII characters, or eight BCDs.

#### **BINARY SUMS**

Working with binary numbers has its good and bad aspects. On the bright side, the rules are fewer than with decimal numbers:

| 1 + 0 = 1  | $1 \times 0 = 0$ | 1 - 1 = 0  |

|------------|------------------|------------|

| 1 + 1 = 10 | $1 \times 1 = 1$ | 10 - 1 = 1 |

The hard part is that binary numbers are not compact; the human eye and brain suffer from reading and remembering 100101001011 compared with its decimal equivalent, 2379.

Let's add two binary numbers together manually, so you can see the rules in action:

$$10111 = \text{decimal } 16+0+4+2+1 = 23$$

+

$$11101 = \text{decimal } 16+8+4+0+1 = 29$$

$$110100 = \text{decimal } 32+16+0+4+0+0 = 52 \text{ (check)}$$

(We proceed from the right: 1 + 1 = 10, so write 0 and carry 1, and so on.)

#### OCTAL AND HEXADECIMAL

We should mention here two other number notations you will encounter, both of which are easily derived from binary notation but which offer more compactness and ease of use.

The octal system uses the base 8, so that only the numbers 0 through 7 are employed, and each column represents a power of 8. Here are a few examples:

| Binary | Octal | Decimal |

|--------|-------|---------|

| 111    | 7     | 7       |

| 1000   | 10    | 8       |

| 100000 | 40    | 32      |

| 111111 | 77    | 63      |

Conversion from binary to octal is very simple. The trick is to partition the binary expression into groups of 3 starting from the right. Then evaluate each group of 3 bits into decimal.

111111 = (111)(111) = (7)(7) = octal 77100101001011 = (100)(101)(001)(011) = (4)(5)(1)(3) = octal 4513

The hexadecimal (short name **hex**) system uses a base of 16, so we need 16 distinct symbols to express numbers in hex. Our usual symbols 0 through 9 are okay for the first ten, then we borrow the letters A=10, B=11, C=12, D=13, E=14, F=15. Here are some examples:

| Binary | Octal | Decimal | Hex |

|--------|-------|---------|-----|

| 111    | 7     | 7       | 7   |

| 1000   | 10    | 8       | 8   |

| 1010   | 12    | 10      | А   |

| 1111   | 17    | 15      | F   |

| 100000 | 40    | 32      | 20  |

| 111111 | 77    | 63      | 3F  |

Once you get used to it, hex is probably the most convenient notation for 16/32-bit computer work. Each hex symbol represents a nibble, two of them make a byte, and so on. Binary-to-hex conversion can be done "at sight" using a similar trick to the binary-octal method just described. Divide the binary number into fields of 4, from the right:

111111 = (0011)(1111) = (3)(F) = hex 3F

An even easier method, if you venture into serious machine-level programming, is to buy an electronic hand calculator with instant binary, octal, decimal, and hex conversion.

Bases higher than 16 have been tried, but what you gain in compactness, you lose in legibility. The mathematician and computer pioneer, Alan M. Turing (1912-1954), was fond of the base 32. This requires, of course, 32 distinct symbols, namely 0 through 9 and the 22 letters A through V, for example. Whence: 1111111111 = 1777 (base 8) = 1023 (base 10) = 3FF (base 16) = VV (base 32). Turing's notation was even trickier since he was tied to the arbitrary 32 characters on his five-channel teleprinter (an early printer, operated from five-track paper tape).

#### SUMMARY OF NUMBER SYSTEMS

Numbers can be expressed using bases other than the familiar base of 10 (decimal system). Binary (base 2), octal (base 8), and hexadecimal (base 16) arise naturally in computer mathematics.

The neat thing about binary numbers is that simple and fast electronic circuits can be built that automatically perform the basic arithmetical operations (add, subtract, multiply and divide) — witness, for example, the aforementioned pocket calculator. The step from on/off switches to arithmetic requires a brief detour into logical operators and Boolean algebra.

#### **BOOLEAN ALGEBRA**

George Boole (1815-64) was the first to develop mathematical rules for logical operations, now known as Boolean algebra.

Logic deals with a particular binary situation since it labels propositions true or false. Boole therefore assigned the numeric symbols 1 for true and 0 for false, and then studied the rules for combining these using the logical operators NOT, AND and OR in place of the familiar arithmetical operators.

As in everyday "logic," if the propositions A and B are *both* true, we say that the single proposition (A AND B) is true. If either or both A and B are false, then we say (A AND B) is false. Similarly, if A is true, we say that (NOT A) is false. We commonly use the symbols

Replacing true and false with 1 and 0, the rules turn out to be similar to binary arithmetic with " $\land$  = multiply" and " $\lor$  = add" but there are some subtle differences:

| Logic           |         | Boolean          | Binary           |

|-----------------|---------|------------------|------------------|

| false OR false  | = false | $0 \vee 0 = 0$   | 0 + 0 = 0        |

| true OR false   | = true  | $1 \lor 0 = 1$   | 1 + 0 = 1        |

| false OR true   | = true  | $0 \vee 1 = 1$   | 0 + 1 = 1        |

| false AND false | = false | $0 \wedge 0 = 0$ | $0 \times 0 = 0$ |

| true AND true   | = true  | $1 \wedge 1 = 1$ | $1 \times 1 = 1$ |

| true AND false  | = false | $1 \wedge 0 = 0$ | $1 \times 0 = 0$ |

| false AND true  | = false | $0 \wedge 1 = 0$ | $0 \times 1 = 0$ |

So far, so good! But the rules diverge with:

| Logic               | Boolean          | Binary                    |

|---------------------|------------------|---------------------------|

| true OR true = true | $1 \wedge 1 = 1$ | 1 + 1 = 10                |

| NOT(true) = false   | $\sim 1 = 0$     | 1's complement of $1 = 0$ |

| NOT(false) = true   | $\sim 0 = 1$     | 1's complement of $0 = 1$ |

#### **COMPOUND LOGICAL OPERATORS**

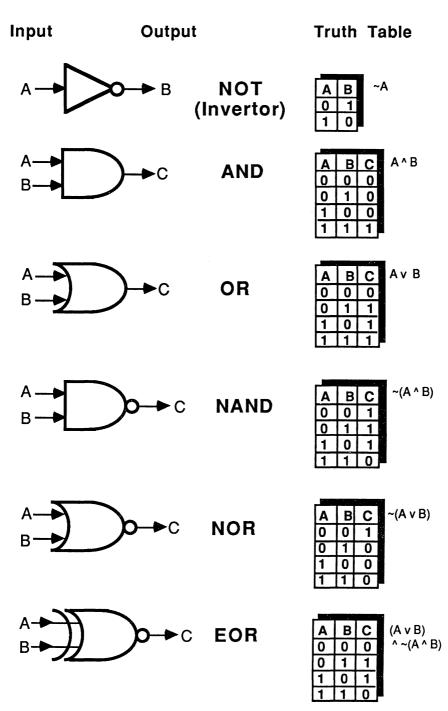

Various compound logical operators can be defined in terms of AND, OR, and NOT. For instance NOT and AND can be combined to give NAND. The tables below (known as truth tables, since they never lie), show the compounds you'll meet in computer schematics and programming situations:

|    |   | AND           |     |               |     |               | NAND (Not AND) |   |   |               |   |            |

|----|---|---------------|-----|---------------|-----|---------------|----------------|---|---|---------------|---|------------|

|    |   | Α             | В   |               | A∧B | 3             |                | А | В |               |   | ~(A∧B)     |

|    |   | 0             | 0   | $\rightarrow$ | 0   |               |                | 0 | 0 | $\rightarrow$ | • | 1          |

|    |   | 0             | 1   | $\rightarrow$ | 0   |               |                | 0 | 1 | $\rightarrow$ | • | 1          |

|    |   | 1             | 0   | $\rightarrow$ | 0   |               |                | 1 | 0 | $\rightarrow$ | • | 1          |

|    |   | 1             | 1   | $\rightarrow$ | 1   |               |                | 1 | 1 | $\rightarrow$ | • | 0          |

| OF |   |               |     |               |     | Not (         |                |   |   | Exclu         |   | -          |

| A  | B |               | A∨B | A             |     |               | ~(A∨B)         | A | B |               |   | √B)∧~(A∧B) |

| 0  | 0 | $\rightarrow$ | 0   | 0             | Ū   | $\rightarrow$ | 1              | 0 | 0 | $\rightarrow$ | 0 |            |

| 0  | 1 | $\rightarrow$ | 1   | 0             | -   | $\rightarrow$ | 0              | 0 | 1 | $\rightarrow$ | 1 |            |

| 1  | 0 | $\rightarrow$ | 1   | 1             | 0   | $\rightarrow$ | 0              | 1 | 0 | $\rightarrow$ | 1 |            |

| 1  | 1 | $\rightarrow$ | 1   | 1             | 1   | $\rightarrow$ | 0              | 1 | 1 | $\rightarrow$ | 0 |            |

The exclusive OR gives true when either input (but not both) is true. In normal speech we do not always distinguish between these two meanings of OR. So everyday "logic" is not always precise enough for "reasoning" with a computer.

#### **PROGRAMMER'S LOGIC**

The precision of Boolean algebra is a vital part of the programmer's life, since we are often interested in getting the system to test the outcome of a routine (true or false) and then perform different programs according to the result. An example familiar to all those who have ever tackled a tax form might be:

If you are male, married, over 40, earning less than \$10,000, or female, single, under 50 earning more than \$6,000 complete line 3. Otherwise skip to line 12.

In Boolean terms this requires evaluating an expression like:

(~F x M x A>40 x SAL<10,000) + (F x ~M x A<50 x SAL>6000)

where each individual term, called a Boolean variable or expression, is set to 1 for true and 0 for false. The answer obtained by mechanically following the rules will be 1 for true (so complete line 3) or 0 for false (skip to line 12). Note that if you are male, then F ("being a female") is false = 0, while  $\sim$ F ("not being a female") is true = 1, and so on.

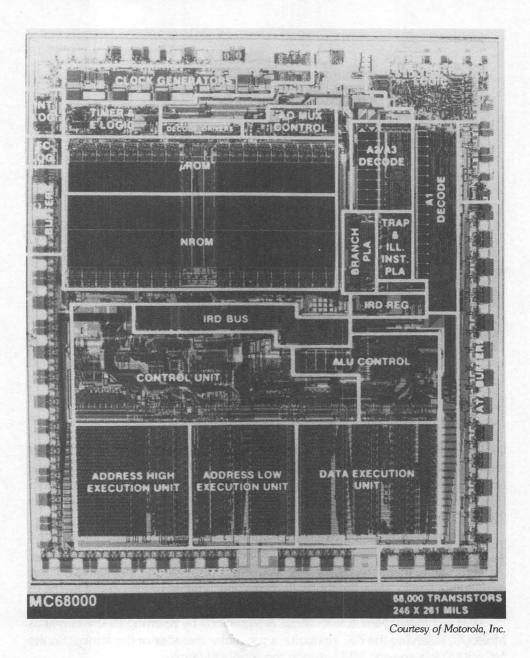

#### LOGIC GATES

Electronically, it is possible to build devices called **gates** that combine signals according to the rules of Boolean algebra. Figure 1-5 illustrates how these are shown in circuit diagrams. In modern micros, these gates are transistors embedded in the silicon. The MC68000, some say by coincidence, has about 68,000 such gates. (The earlier M6800 had about 6,800 transistors, so there may be some logic to Motorola's numbering scheme.) The "1" and "0" can represent any two distinct electrical states, for example "0" may mean a +5 volt signal and "1" may be 0 volts. The NOT function is called an **inverter** since it inverts 0 to 1 and 1 to 0. Gates are the basic building blocks of computers. They can be interconnected in complex patterns to perform a variety of functions, such as decoding and binary arithmetic. IC (integrated circuit) chips are available in tens of thousands of variations offering every conceivable combination of logic for the circuit designer. And if your volume is high enough, a special purpose chip may save you wiring together off-the-shelf chips.

| INP | UT | OUTPUT |   |  |  |

|-----|----|--------|---|--|--|

| A   | В  | S      | С |  |  |

| 0   | 0  | 0      | 0 |  |  |

| 0   | 1  | 1      | 0 |  |  |

| 1   | 0  | 1      | 0 |  |  |

| 1   | 1  | 0      | 1 |  |  |

$$S = Sum = (A \lor B) \land \sim (A \land B) = A \bigoplus B (EOR)$$

$C = Carry = A \land B$

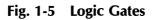

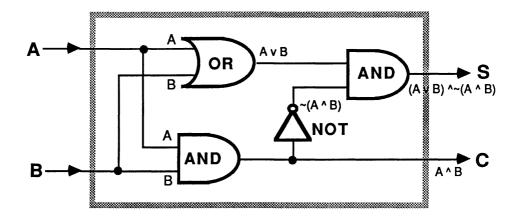

#### FROM GATES TO SUMS

Let's see how Boolean Algebra helps to design circuits which bridge the gap between logic and arithmetic. In Figure 1-6 we show a table for a simple binary A + B adder, where A and B can equal 0 or 1. The outputs are S = sum and C = carry. S and C also take the values 0 and 1, following our rules for binary addition. We note that S is the EOR (Exclusive OR) of A,B, while C is A $\land$ B. The circuit in Figure 1-6 is obtained by replacing the Boolean symbols with their silicon equivalents — 2 AND-gates, 1 OR-gate and 1 inverter. What is even more remarkable is that with IC technology many thousands of such circuits can be integrated into a tiny mass-produced chip.

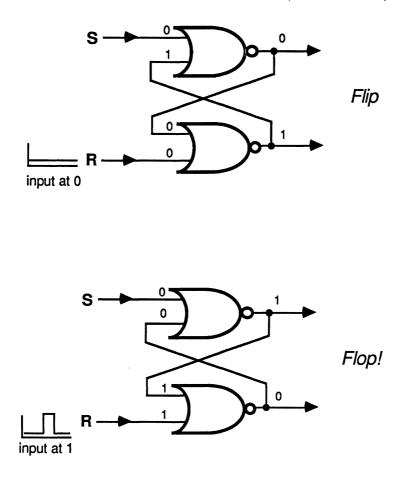

Fig. 1-7 Basic Flip-Flop

The half-adder circuit in Figure 1-6 just adds two bits together, but it is not difficult to cascade similar circuits in series to give full binary addition of 8 or 16 bits depending on the chip's architecture. A full-adder needs three inputs, since it must take in the previous "carry" bit — but the principle is as shown in Figure 1-6.

#### **FLIP-FLOPS**

Before we leave the topic of basic computer circuitry, we want to show you a clever combination of gates which indicates how data can be stored electronically. The **flip-flop** consists of two NOR-gates wired as shown in Figure 1-7. Momentarily pulsing the S (Set) and R (Reset) inputs in different ways causes

the two output lines to flip-flop between 0/1 and 1/0 states. These states are remembered long after the input pulses have disappeared, so we have the basis for storing 1 bit per flip-flop, and the means of reading or writing its value. As with the binary adder, flip-flops can be wired together in wondrous ways to provide fast on-chip storage units known as **registers**.

#### SUMMARY OF GATES AND BINARY SUMS

We have seen, in very general terms, that the basic logical operators, AND, OR, and NOT, and their compounds NAND, NOR, and EOR, all have silicon analogues called gates. These gates can be interconnected to perform more complex functions, including binary addition and register storage.

To coordinate these networks of gates, we need another ingredient — time.

#### **CLOCKS**

The frozen-frame 1's and 0's shown as inputs A, B, S, and R in Figures 1-6 and 1-7 actually arrive as a stream of high-speed electrical pulses synchronized by a system clock. This quartz-controlled clock (which may be part of the MPU chip or a separate chip) sets the pace for a host of MPU activities. Generally speaking, the faster the clock, the faster the computer. A typical MC68000 clock would run at 8 MHz (8 million cycles per second) giving a cycle time of 125 nanoseconds (a nanosecond is a billionth of a second — 1/1,000,000,000 sec. This is the time it takes light to travel approximately 1 foot).

#### MICROCOMPUTERS — THE THREE COMPONENTS

We can now take a look at the overall organization of a typical microcomputer system, so we can identify the main elements prior to discussing each in detail. We will find that a microcomputer can be viewed as "three black boxes on a bus".

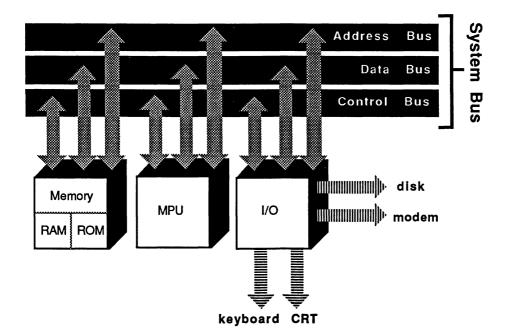

#### SYSTEM BUS

Figure 1-8 shows the system bus, a sort of wiring freeway, through which the major components, labeled MPU, memory, and I/O communicate with each other.

Fig. 1-8 Microcomputer System Bus

#### Memory

The box marked *memory*, subdivided into RAM and ROM, represents the main *immediate* storage for data and programs. Each piece of memory is assigned a unique address allowing fast, random access by the MPU. ROM is read only memory, whereas RAM (Random Access Memory) can be read from or written to.

#### I/O — Input/Output

The single black box marked I/O (input/output) covers a multitude of devices — disk units, user terminals, printers, modems and so on — each with its own particular interfacing hardware circuits (known as I/O controllers) supported by dedicated software such as terminal drivers. I/O is the area of most direct visibility and concern to the average user. In the midst of our microelectronic delving we must not lose sight of the average user, keying in data and printing pie charts.

The system bus carries three kinds of **signal traffic**: **data**, **address** and **control**. In some computers these three sets of signals are electrically independent (separate wires). We call these multibus systems, since one can identify a data bus, an address bus, and a control bus. Cheaper, slower systems may have

a single bus that is shared among the three, using a technique known as multiplexing.

#### **Microcomputer Operation**

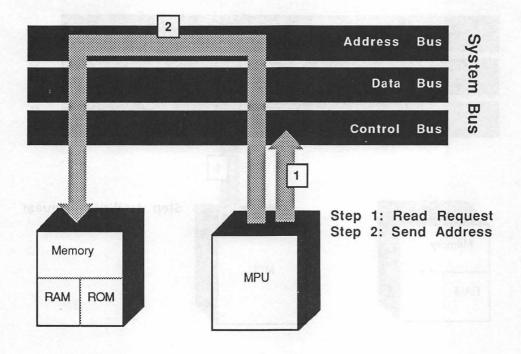

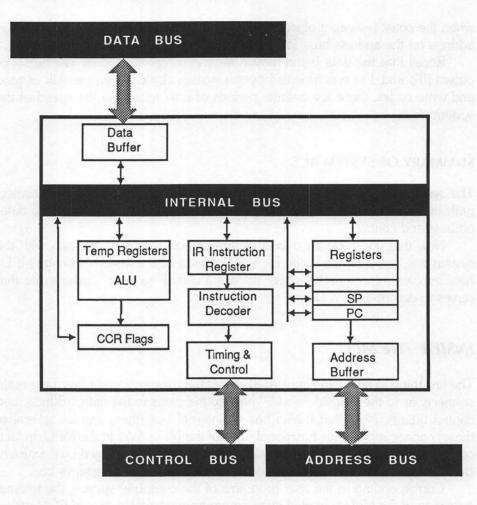

In a read cycle, (Figure 1-9) the MPU seeks data (numbers or instructions) from memory or I/O by sending appropriate request signals down the control bus. If the bus is busy doing something else, the MPU may have to stand by for a few cycles (we call this a *wait* state).

If and when the bus is free, the MPU places an address on the address bus. This address is decoded by circuits in the memory or I/O interface and, if all goes well, the data found at the requested address is moved from memory or I/O to the data bus. The control bus then signals to the MPU that the data is available on the data bus. Once the data is transferred to the MPU's data buffer, the control bus signals that the system bus is free. In a moment you'll see how the MPU handles the incoming data.

The width of the data bus (measured in bits) dictates how much data can be fetched during each read cycle — so the wider the better. You'll see that the size of the data bus plays a vital role in determining the flexibility, performance, and the *cost* of an MPU. The cost element stems from the fact that each bit of the data bus needs a corresponding pin on the MPU chip and associated pathways within the chip.

When people talk about 8-, 16-, and 32-bit computers without further qualification, they *should* be referring to the width of the MPU's data path. But note that some salespersons have been known to lie. Remember Gerswhin's law : "It ain't necessarily so!"

We really need four sizes to honestly characterize an MPU: data width, ALU (Arithmetic/Logic Unit) width, register width, and address width, but life is so short. Who wants to buy an 8/16/32/20-bit micro? (That's the MC68008, by the way.)

The width of the address bus determines the total number of distinct memory (including I/O) addresses that can be accessed and hence affects the maximum memory size. As with data width, the wider the better, but also the more expensive. Here we can make use of our earlier messages-per-bit theory. Most of the 8-bit MPUs have a 16-bit address bus that, as we've seen, allows a maximum of 64K memory addresses (each of which normally accesses an 8-bit byte), since  $2^{16} = 65,536 = 64K$ .

Although there are many clever ways of fitting more than 64K of memory on a 16-bit address bus, they all add overhead in time or cost. The M68000 family has address widths in the range of 20 to 32 bits, giving memory addressing spaces from 1 Mbyte to 4 Gbytes.

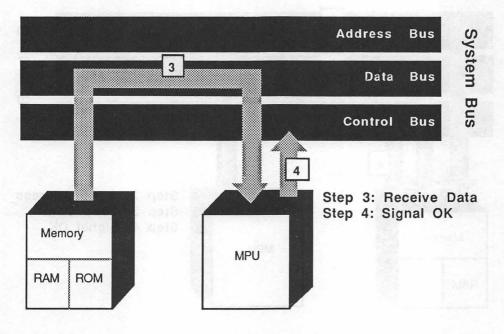

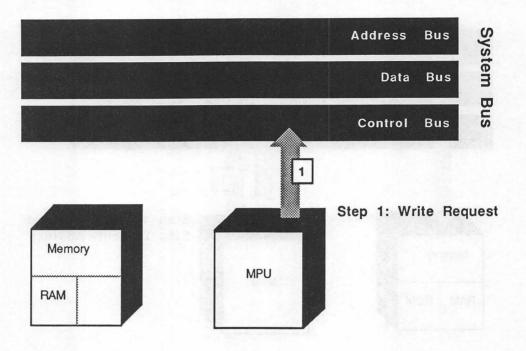

The write cycle (Figure 1-10) allows the MPU to send data to memory or I/O. The MPU signals its intentions (*request to write*) on the control bus, and

#### Fig. 1-9 Read Cycle

Fig. 1-10 Write Cycle

when the coast is clear, it places the data on the data bus, and the destination address on the address bus. The MPU can then carry out its next instruction.

Recall that the data being moved around is represented by fast bursts or pulses (0's and 1's) synchronized by the system clock. When we talk of read and write cycles, these are definite periods of time related to the speed of the system clock.

#### SUMMARY OF SYSTEM BUS

The system bus links the main units of the computer, providing an electrical path between MPU, memory and I/O. It carries three types of signals: data, address and control.

Now that you have an overall picture of how the MPU interacts with the system bus, you can look inside the MPU and see how it works. Although MPUs have evolved into myriad designs, there is a useful "generic" architecture that serves to describe them all.

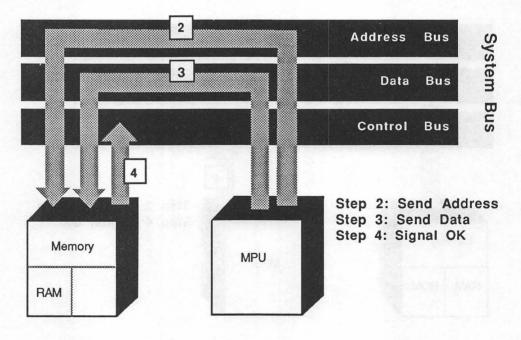

# **INSIDE THE MPU**

The first thing to notice in Figure 1-11 is that the microprocessor has three main connections to the "outside world," namely the paths to the data, address, and control busses. Note that it also has an internal bus (there can be several of these) connecting various functional units of the MPU. Within the MPU, in fact, control and data signals move along the internal bus, synchronized by the system clock — not unlike the picture we drew of the traffic on the system's bus.

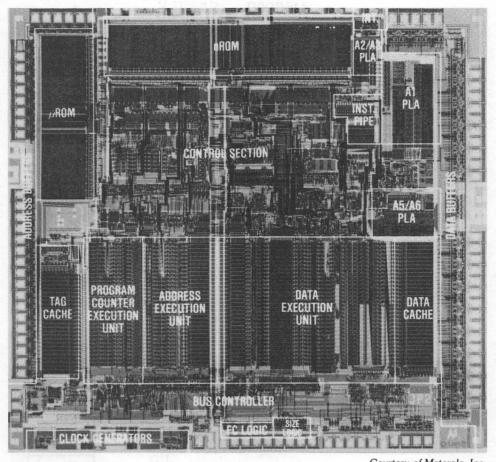

Corresponding to the user programs of the computer system, the internal operation of the MPU is guided by microprograms stored in special ROM within the chip. (This is true of the M68000 and many other MPUs; other MPUs employ hard-wired control logic.)

Let's run through a typical sequence of events.

1. Instruction Fetch: The program counter (PC) is a special register that holds the memory address of the next instruction. Placing this address on the address bus and calling a read cycle will fetch this instruction over the data bus and load it into the instruction register (IR), via the internal bus. Instructions, briefly, are words (or groups of words) that represent the steps of the program stored consecutively in memory. Each instruction is encoded to perform a particular operation, such as ADD or MOVE, on one or more specified operands. For an ADD instruction, for instance, the operands would be the two numbers to be added. A MOVE instruction would specify the operand to be moved (the **source**) and the place it is to be moved to (the

Fig. 1-11 Microprocessor Schematic

**destination**). Once the instruction has been fetched, the program counter is incremented so that it "points" to the next instruction in memory.

- 2. Instruction Decoding: The instruction word passes from the IR to the instruction decoder, which "decides" from the incoming bit-patterns what operation is needed. Typically, the instruction also contains addressing information for the operands, that is, which register or memory location holds the data to be operated on.

- 3. Data Fetch: Determining where the operands are often involves some arithmetic to calculate the operand addresses from the information included in the instruction. For some multiword instructions there may have to be another

instruction fetch, as in step 1 above. It may now take one or more **read cycles** to bring in the operands from memory, or to transfer them from registers. The operands will be routed along the internal bus(ses) to temporary registers.

4. Execute Cycle: The microprocessor is now, hopefully, ready to execute the instruction. The MPU "knows" what to do, where, and to whom. More often than not execution will involve the ALU (Arithmetic/Logic Unit). The answer will be routed via the internal bus to a register, or to the data bus buffer en route to memory. In the latter case, a write cycle will be initiated using the destination address specified in the instruction. The ALU also sets a flag register (also known as a condition code register) according to certain conditions arising from the operations (result negative, result zero, overflow and so on).

Having completed steps 1 through 4, the MPU is all set to do the same for the next instruction — since you saw that the PC (Program Counter) has already been increased, and therefore has the address for this next instruction. Remember that instructions are normally stored in successive memory locations.

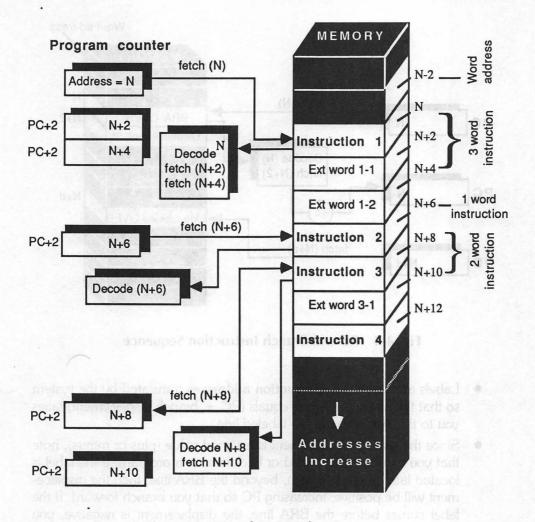

Among the many deviations possible from the simple sequence listed above, a common one involves **branching**. In branching, some program condition arises that calls for the execution of an instruction out of normal sequence. Branching is achieved by setting a new address in the PC.

Other deviations can arise from errors, exceptions, and interrupts from other jobs. These will be covered in later chapters, since the M68000 has some unique features for handling errors and exceptions.

A rather amazing fact is the sheer *speed* with which our four basic steps take place. MPU speed is rated in MIPS (million instructions per second) — of course, not all instructions take the same time, so MIPS can be misleading. A single instruction can take from 4 to over 200 basic machine cycles. The MC68020, to give you an idea, runs at a sustained rate of 2 to 3 MIPS, with occasional bursts of 8 MIPS.

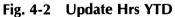

# **PREFETCH AND PIPELINING**

If you look at our four steps — fetch instruction, decode, fetch data, execute — you can imagine a tremendous amount of bus activity, both on the main system bus and on the MPU internal bus. In the never-ending fight to squeeze more performance from a system, the designers obviously attempt to speed up each aspect of the cycle, especially by reducing the possibility of delay (wait states) arising from bus contention or a slow memory access time. But when that has reached practical limits there still remains the possibility of gaining speed by

**overlapping** operations — achieving what is known as **concurrency**. It turns out that several of the steps 1 through 4 can be overlapped — performed simultaneously. A typical **prefetch** strategy involves having three instructions passing through the MPU at any one time — one being executed, one being decoded, and one being fetched. In **pipelining** a greater number of instructions may be passing through. These steps often require different system resources, provided the chip has the necessary buffers and pathways. If, as will happen from time to time, there is a clash or contention, one of the steps will be held up. In Chapter 8 you will see how the instructions at the ready in fast on-chip registers. In many programming situations the same loop is iterated many times; the instruction cache can reduce the fetch time considerably.

Let's review in more detail some of the main boxes in Figure 1-11, and then see how memory is organized.

#### **ARITHMETIC/LOGIC UNIT**

An area of the MPU designed specifically for arithmetic and logical operations is called an arithmetic/logic unit (ALU). Advanced MPUs like the M68000 have several independent ALUs. The width of the ALU, 16 bits for the MC68000, for example, tells you how many bits can be added together in parallel, at one time. Larger numbers, of course, can be handled by taking extra clock cycles.

You saw earlier how gates could be combined to perform binary addition. It is not too difficult to extend these to perform the other basic arithmetical operations.

Subtraction is equivalent to adding a complement (easily obtained with inverters); multiplication is repeated addition (although it is sometimes performed from preset tables); and division is repeated subtraction and testing for zero.

Hardware division, incidentally, is one of the many mainframe features now appearing as standard on the 16/32-bit micros. The alternative on most of the 8-bit micros, dividing by software, is tedious and much slower. Similarly, the M68000 offers hardware BCD (Binary Coded Decimal) arithmetic as well as a useful repertoire of shifts, rotates, and extended arithmetic. The latter involves several clever multi-precision aids for doing sums across several registers for increased accuracy.

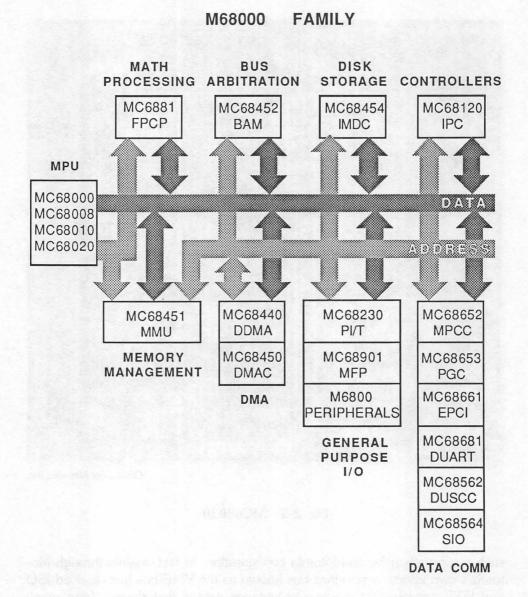

#### MATH COPROCESSORS AND THE MC68881

For heavy number crunching using floating-point format, Motorola introduced the MC68881 math coprocessor, which is fully compatible with the M68000

range (indeed the MC68881 is a chip in the same range of complexity as the MC68000).

Coprocessing differs from multiprocessing in the way that the work load is shared. Any suitably interfaced MPU in the system, on decoding an instruction calling for floating point, will pass that instruction over to the MC68881 — so coprocessors actually share the same instruction stream. Multiprocessors normally do their own thing from independent programs, although they can and do interact by sharing data and passing signals (known sometimes, rather pleasantly, as semaphores) via memory.

Simply stated, you can look on the ALU as the calculating center of the chip, capable of seeking help from a math coprocessor.

Inputs to the ALU are numbers from temporary registers (or buffers) via the internal data bus together with control signals, (instructions indicating the calculation or logical operation required). Output from the ALU, the results of the calculation plus various control and routing signals, flow back to other parts of the MPU via buffers and the internal bus. An important source for ALU data input, as well as a destination for ALU data output is a special area of on-chip fast memory, organized into fixed length **registers**. Unlike the temporary registers and buffers, these are accessible to the programmer.

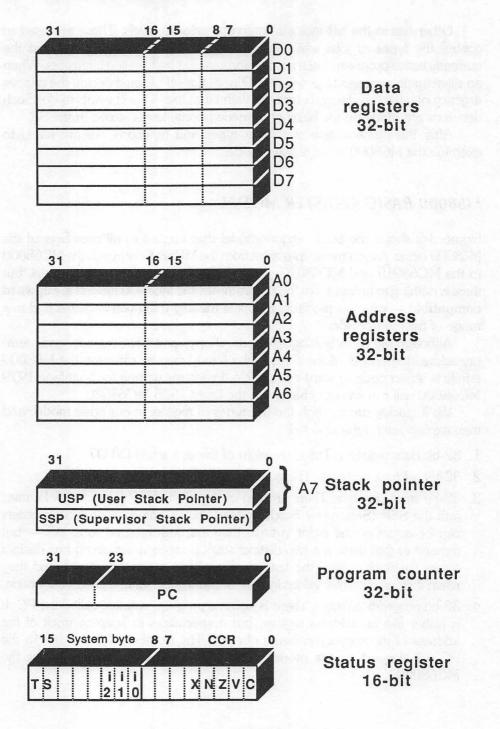

#### REGISTERS

Registers play a major role in giving an MPU its personality and programmability, and they come in all shapes, sizes, and flavors. The basic MC68000 has 17 general-purpose registers, each 32 bits wide. In Chapter 3 we will cover this aspect in depth, since the instruction set and the way the registers are organized are intimately related.

# **MEMORIES ARE MADE OF THIS**

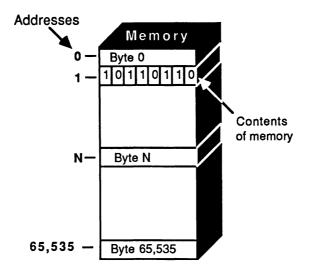

The normal fast immediate memory for modern computers is the RAM (Random Access Memory) chip. RAM Chips come in various sizes and are plugged into memory boards to give a total capacity per board from 16 K-bytes up to 2 M-bytes. A system may well have more than one memory board within it. The physical arrangement of memory is usually of no concern to the programmer, who is interested only in the logical addressing scheme.

You should remember, in passing, that a growing number of peripherals will have local RAM and/or ROM, outside the main MPU addressing space. Typical examples are buffers for printers, keyboards, and CRT displays.

Fig. 1-12 Addressing 64 K-Byte Memory

# ADDRESSING MEMORY

As you saw in the read/write cycles, the main characteristic of RAM is that the MPU can read and write data from and to RAM. To determine which of the many byte locations it needs to access, each byte (or group of bytes) is given an address. A 64K-byte memory can be thought of as 65,536 mailboxes, numbered 0 thru 65,535. Inside each mailbox is a byte (8 bits) holding data (256 possible characters, remember).

# WHAT ARE WE READING?

If the computer were to read from byte address 1 (see Figure 1-12), it would fetch the byte 10110110. What would this mean? Well, almost anything! Out of context the byte has no specific meaning. If the computer were expecting a number it could be either

10110110 = decimal 182 (unsigned)

or

10110110 = decimal -74 (signed 2's complement)

If the byte were part of a 7-bit ASCII string, the leftmost bit could be a parity bit with the remaining 7 bits giving the numeric character "6". Or it might be a full 8-bit ASCII graphics character or "private" control code.

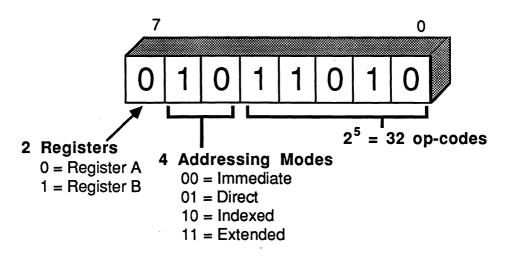

If the MPU were reading a program, the byte would be interpreted as part of an instruction. The words and bytes that make up instructions have their own peculiar coding schemes built into the MPU. You saw that the instruction decoder has to interpret this code before the MPU can execute it. In Chapter 4, you will see how the M68000 instruction set is encoded into groups of 16-bit words. Recall that each 16-bit word offers up to 65,536 messages, so we have the basis for a very rich and varied set of different operations.

Since the bytes we read from memory can mean so many different things, you may be wondering how the MPU distinguishes all these possible interpretations. The answer lies in the program itself. And the reason that program bugs can produce such bizarre results is because the MPU will blindly interpret each byte as requested. So if you inadvertently ask the system to execute rather than print an ASCII character, it is likely to do strange things.

#### IMPORTANCE OF MEMORY SIZE AND SPEED

Memory size and speed play a vital role in every aspect of computing. At the simplest user level the amount of memory can dictate both the types of job you can run and the speed with which they are performed. A RAM or ROM that is not matched to the speed of the MPU can, as we've seen, induce wait states in the MPU. Too little memory can often bring the system to a halt with a sneering "insufficient memory" message on your screen. Some programs need to be completely **resident** in RAM before they can run at all. Other programs are arranged to run with just portions of the code in RAM and are smart enough to pull in **overlays** from a disk. Overlays overwrite sections of code in RAM once they have served their purpose. Very large programs can theoretically be made to run in very small memories, but the overhead caused by constant **swapping** can create some ennui for the user.

# MEMORY MANAGEMENT

Our simple picture of memory sitting on an address bus deliberately evades many complex problems concerning the interactions between the MPU(s), system and user programs, and memory access. These are particularly severe when the system allows **multitasking**, that is, the "simultaneous" running of several jobs, or different parts of the same job. Clearly, care must be taken to prevent one task from intruding on the memory allocated to another task.

In particular, the **operating system** (OS) which is overseeing all user tasks, is itself running tasks, (including the task of scheduling tasks) and its system memory space must be secure from accidental or deliberate intrusion. Users

may bithely kill each other's jobs, but if the OS goes, we all go. What makes the system memory sacrosanct is not only the programs resident there (OS, compilers, utilities), but also vital system data, such as tables for handling interrupts and exceptions, and an area known as the **system stack** which holds transient information concerning the status of interrupted jobs.

Even a single-user, single-MPU system nowadays frequently offers many levels of concurrency. The speed of the modern MPU, compared with the speed of most I/O devices, allows it to service many requests in sequence, so quickly that each job is convinced it has the MPU's undivided attention.

There is considerable diversity in the methods used to partition memory safely and economically, and much debate on the merits of various approaches. The initial problem is that of mapping physical to logical memory. By this we mean relating the physical memory addresses as "seen" by the address decoders, with the logical addresses presented to the MPU by the programmer.

Some MPUs, like the Intel 8088/8086, have the solution to this problem designed into the silicon, while others (like the M68000) leave all the options open to the system designer.

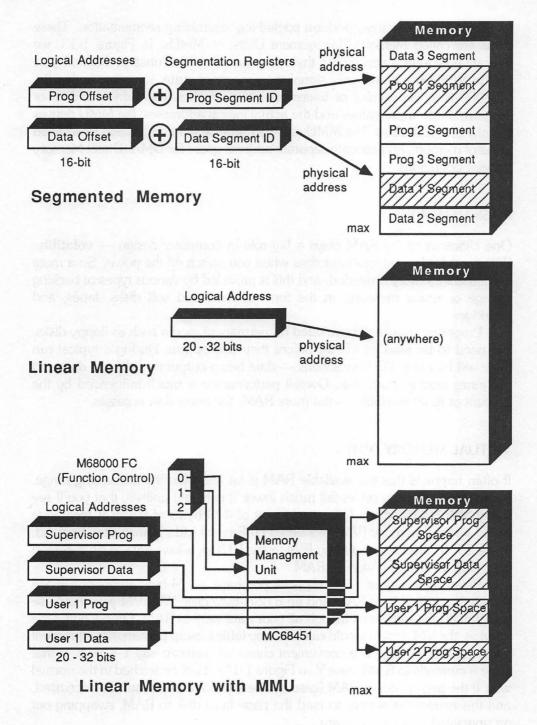

#### SEGMENTED MEMORY

The Intel approach is called **memory segmentation**, as opposed to the Motorola **linear** memory philosophy. In a segmented memory, the programmer looks at several exclusive, fixed memory spaces (or segments), typically 64 K-bytes each. As shown in Figure 1-13, the logical addresses he or she uses are offsets, modified by the MPU to obtain the physical addresses. The modification is achieved by adding values (called segment identifiers) held in segmentation registers, and this can be done in such a way that the user's programs and data are kept apart, safe from other users. The advantages are the security and speed that arise from the use of short 16-bit addresses. The disadvantage is the overhead involved in checking and adding the segment identifiers.

# LINEAR MEMORY AND THE MMU (MEMORY MANAGEMENT UNIT)

In the linear approach the programmer looks on memory as one long continuous addressing space from zero to the maximum possible address, addressed by means of a single number. With the 20- to 32-bit address widths available on the M68000, this represents a generous chunk (from 1 M-byte to 4 G-bytes) to play with. Within this maximum, jobs can be allocated the optimum memory size needed. Security must be "supplied" externally, as it were, but the M68000 is designed to facilitate this. Several specialized chips, such as the MC68451

Fig. 1-13 Segmented and Linear Memories

(available from Motorola) perform something resembling segmentation. These chips are called Memory Management Units, or MMUs. In Figure 1-13, we indicate how MMUs accomplish their purpose. The FC (Function Control) pins on the M68000 automatically signal the **processor state**, namely whether the M68000 is in **supervisor** or **user**mode, and whether the address is data or program. From these values and the actual logical addresses, the MMU derives the physical addresses. The MMU can also provide write-protection to selected areas of memory, and allocate separate address space for DMA (Direct Memory Access) operations.

#### MASS MEMORY

One characteristic of RAM plays a big role in computer design — volatility. With most RAM, you lose your data when you switch off the power. So a more permanent memory is needed, and this is provided by various types of backing storage or **mass memory**, in the form of hard and soft disks, tapes, and cartridges.

Programs are usually marketed on permanent media such as floppy disks, but need to be read into RAM before they can be run. During a typical run there will be many I/O transactions — data being output to disk, and data and programs read in from disk. Overall performance is much influenced by the amount of RAM available — the more RAM, the fewer disk accesses.

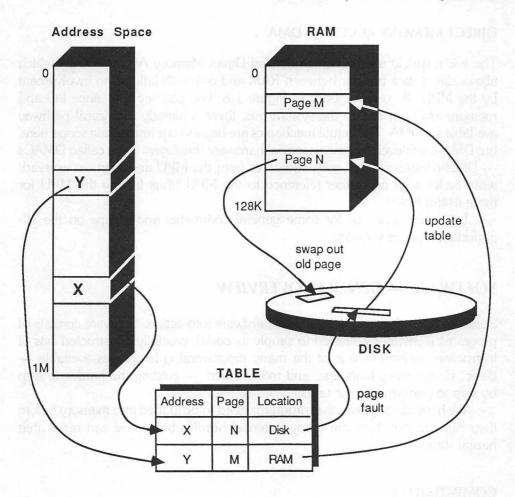

# VIRTUAL MEMORY (VM)

It often happens that the available RAM is far less than the addressing range. In fact, until memory prices fall much lower, it is highly unlikely that you'll see many MC68020s with a full complement of 4 G-bytes of RAM! A technique called **virtual memory** (VM) pioneered by Ferranti Ltd., Manchester, England, in the 1950s (and reinvented by IBM in the 1970s), allows data to be accessed from disk as though it were in RAM.

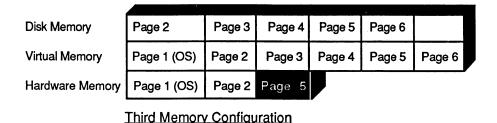

Referring to Figure 1-14, suppose you have a 1 M-byte addressing space (20 bits), a 128 K-byte RAM and an 872 K-byte disk. With VM you could use your full 20-bit address as though all your data were in RAM. On decoding the address, the VM system would calculate (by table lookup perhaps) its equivalent page number. A page is a convenient chunk of memory, say 1 K-byte. If that page is currently in RAM (case Y, in Figure 1-14), it will be fetched in the normal way. If the page is not in RAM (case X), we say that a **page fault** has occurred, and this causes the system to load the page from disk to RAM, swapping out an unwanted page if necessary.

Fig. 1-14 Virtual Memory

Chapters 7 and 8 will discuss virtual memory in more detail, as implemented on the MC68010 and MC68020.

# **RAM DISK**

in dan .....

The opposite to VM is the RAM disk. If your program is written to access files from a disk, and you have plenty of RAM to spare, it is possible to increase performance by loading your files into RAM. The RAM disk software then fools the program into treating RAM like a disk. The starting memory address of each file record can be calculated — provided, naturally, that the disk formatting rules are known.

#### DIRECT MEMORY ACCESS — DMA

There is a widely used technique called Direct Memory Access (DMA) which allows direct data transfer between RAM and disk with little or no involvement by the MPU. If you look back to Figure 1-8, you can see that since I/O and memory are both tied to the system bus, there is already a physical pathway available for DMA. The actual mechanics are beyond our immediate scope here, but DMA is achieved by having special hardware (intelligent chips called DMACs — DMA controllers) that grab addresses from the MPU and then set up read/write cycles with no further reference to the MPU (thus freeing the MPU for more useful tasks).

Let's take time out for some general comments and recaps on the allimportant topic of software.

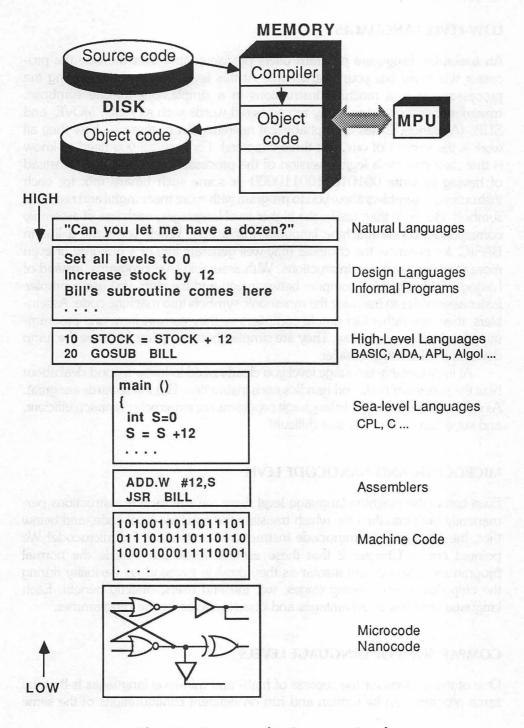

# SOFTWARE — GENERAL OVERVIEW

Software is needed to goad the inert hardware into action. Software consists of programs (sometimes referred to simply as **code**), carefully constructed lists of instructions written in one of the many programming languages available — Basic, C, assembly language, and many others — guiding the hardware step by step to perform specific tasks.

We have already seen that programs need to be loaded into memory before they can run but there are many potential hurdles before we can reach that happy state.

#### COMPATIBILITY

An essential concept throughout the industry is compatibility — the idea of hardware and software elements throughout the **system** working together in harmony. We will reserve the word *system* for an organized matching set of devices and programs.

Hardware and software exist today in a dazzling profusion of shapes, flavors, and sizes, and creating a system from diverse components, even when you buy from a single manufacturer, is no trivial matter.

**Portability** in hardware simply means that the thing has a handle and weighs less than 100 pounds; software portability is a less tangible concept. A program written to run on many different systems is clearly more marketable, although sometimes you lose efficiency by aiming at portability.

A group of related programs is often called a **package**. Well-known packages such as WordStar<sup>®</sup> and Lotus<sup>™</sup> 1-2-3<sup>™</sup> offer one specialized application

(word processing and spreadsheets, respectively). A more recent fashion is the **integrated** software package such as Symphony<sup>™</sup> which provides both word processing and spreadsheets. Financial data from the spreadsheet can be transferred automatically to the WP program in order to produce neatly typed reports.

If you want your computer to run your payroll, you'll need to load a payroll package that specifically and in minute detail tells the computer how and when to calculate each element of tax deduction, where to find the various tables, and so on. The hardware has no preconceived notions regarding your wages and is blissfully unaware of the IRS. When we talk about the computer as a general purpose machine, we mean that it can do anything — as long as we have the appropriate compatible software.

#### APPLICATIONS SOFTWARE

The payroll programs mentioned above belong to what we call **applications software**. Applications software is aimed at solving particular user problems.

#### SYSTEMS SOFTWARE AND THE OS

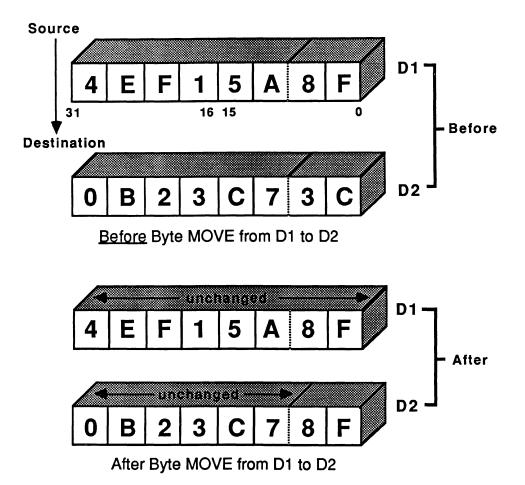

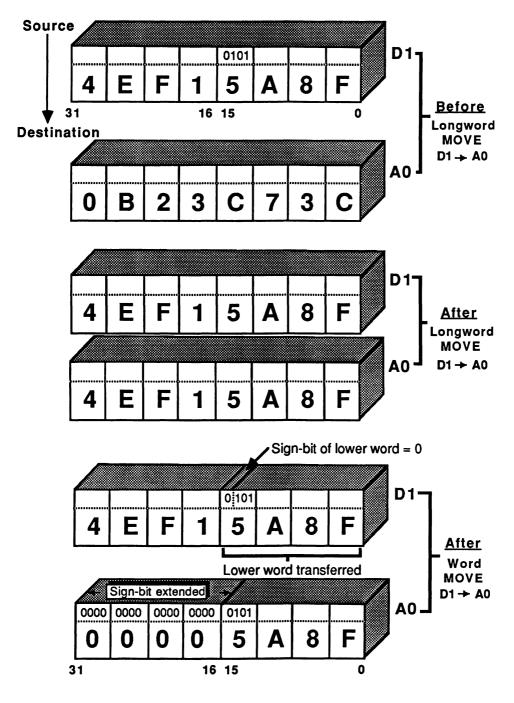

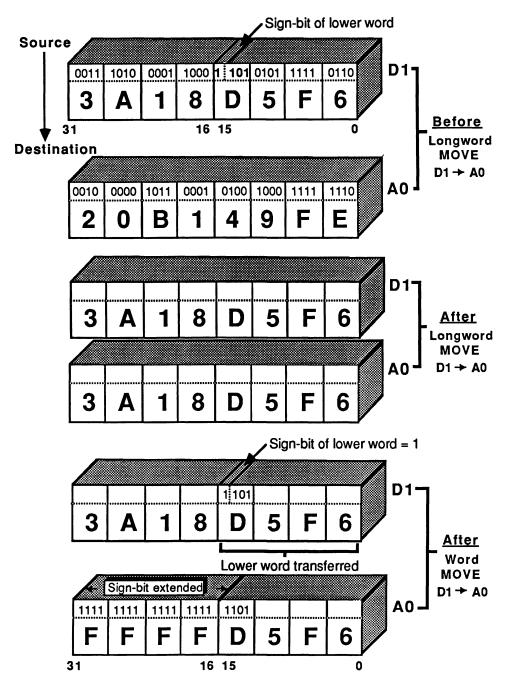

The computer also needs **systems software** to handle a variety of basic support functions required by every applications program, such as resource allocation, controlling peripherals, and so on. These support programs, known as **utilities**, are often lumped together under the title OS (Operating System), pronounced "Oh-ess." Without the OS, each applications program would have to know the exact hardware configuration and include all these tiresome details. In the early days of computing, in fact, there were no operating systems, and the programmer just had to code everything. The OS frees the programmer from many **housekeeping** chores. Furthermore, each OS provides its standard way of communicating with the computer and isolates the programmer from many machinespecific features.